基于FPGA的PCM-FM遥测中频接收机设计与实现

2.5 硬件设计

接收机以FPGA为中心,外围为晶振、电源模块、A/D转换电路和USB接口电路。

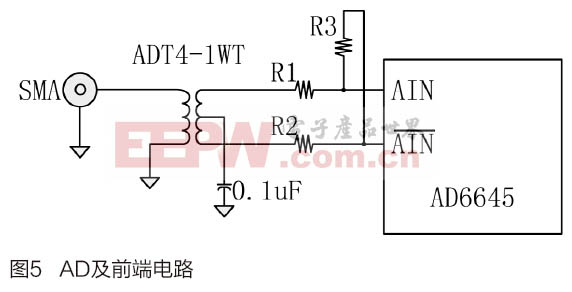

AD转换设计采用AD6645,AD6645是采用CMOS工艺的14位模数转换器,最高采样率为105MSPS,在中频为70MHz时的SNR为73.5dB,SFDR为89dBc,模拟带宽达200MHz[6]。AD模拟输入端为差分输入,通过阻抗比4:1的变压器进行交流耦合,电路原理图见图5。图中R1=R2=24.9Ω,R3=178Ω,输入端匹配阻抗为50Ω。AD时钟管脚与FPGA相连,采样频率由FPGA控制,本设计采样频率为40HMz。

FPGA选用Xilinx Spartan-6系列XC6SLX100工业级FPGA芯片。该芯片采用45nm工艺,专为低成本与低功耗而精心优化,集成了丰富的逻辑资源,接口可选择使用1.2V、1.5V、1.8V、2.5V或3.3V多种标准,便于与其它电路接口[7]。XC6SLX100 FPGA的配置文件大小为26,543,264bits,配置芯片选用XCF32P,采用BASIC Master Serial 配置模式,配置时钟由FPGA内部提供,配置速率22MHz。

遥测中频接收机与上位机之间采用USB接口,接口芯片选用CY7C68013,FPGA与CY7C68013间采用SlaveFIFO通信模式。

3 测试结果

搭建测试平台,遥测接收系统由射频接收机、本文设计的中频接收机、上位机等组成。中频接收机测试结果:最大多普勒频偏250kHz、码速率100kbps~5Mbps可调、抗连续连0或连1可达128位、帧长与帧同步码可灵活设置。结果表明满足设计指标要求。

4 结论

本文设计了一款基于FPGA的PCM/FM 遥测中频接收机,码速率、帧长、帧同步码等可灵活设置,硬件结构简单,可单板实现,达到小型化、低成本设计目的。目前,该接收机已服务于多个项目,性能稳定可靠。

参考文献:

[1] 李英丽,刘春亭.空空导弹遥测系统设计[M].北京:国防工业出版社,2006

[2] Uwe Meyer-Baese.数字信号处理的FPGA实现[M].北京:清华大学出版社,2002

[3] Miao G J.Signal processing in digitai communications [M].Artech House Inc,2007

[4] 樊昌信,詹道庸,徐炳祥等.通信原理(第四版)[M].北京:国防工业出版社,2001

[5] 夏利利,刘冰,周江等.PCM遥测帧同步技术性能分析[J].电讯技术,2014, 54(6):803-807

[6] AD6645 Data Sheet,Analog Device Inc,2002

[7] Xilinx Inc.Data Sheet,Spartan-6 Family Overiew,2010

遥测系统 中频接收机 位同步 帧同步 FPGA 201506 相关文章:

- 基于trf4400的心电数字无线遥测系统(01-03)

- 德州仪器——零中频接收机设计(09-24)

- 数字接收机中位同步器的研制 (08-29)

- 高速移动条件下位同步器的设计(05-26)

- 基于叠加训练序列光OFDM系统帧同步算法FPGA实现(04-17)

- 基于FPGA的短波通信接收机(11-19)