直接数字合成技术实现函数信号发生器

一种模式,最后波形信号由输出级输出。

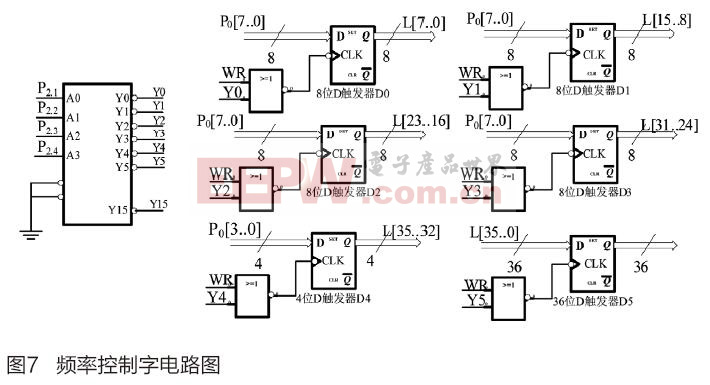

3.3.1 频率控制字电路

由于相位累加器需要输入36位二进制数,因此需要通过时序来控制扩展电路的位数。

如图7所示,4个8位D触发器和1个4位D触发器D0~D4,D0~D4的输出端按顺序接到36位的D触发器D5上,用写信号WR和译码器输出信号Y作为D触发器的时序信号,当WR和译码器信号Y的一路同时为低电平时,即D触发器时钟的上升沿到达时,P0口的数据就通过选通D触发器送出。按照这样,将4组8位二进制数和1组4位二进制数依次送到触发器D0~D4,当WR和译码器信号Y5同时有效时将36位数据同时送入触发器D5。

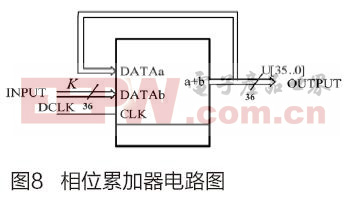

相位累加器是整个DDS系统的核心,它设计的好坏直接影响着整个系统的功能和性能。电路如图8所示。从工作情况看,它实际上是一个带反馈的36位加法器,输出数据反馈到加法器的一个输入端DATAa,在时钟的作用下与输入到另一个输入端DATAb的频率控制字K相加,结果由输出端输出。输出结果一方面又反馈到输入端,另一方面将为后续电路提供输入信号。DCLK为DDS系统时钟输入端,它是由锁相环倍频分频输出提供的,OUTPUT为相位累加器的输出端,输出值用U[35..0]表示。

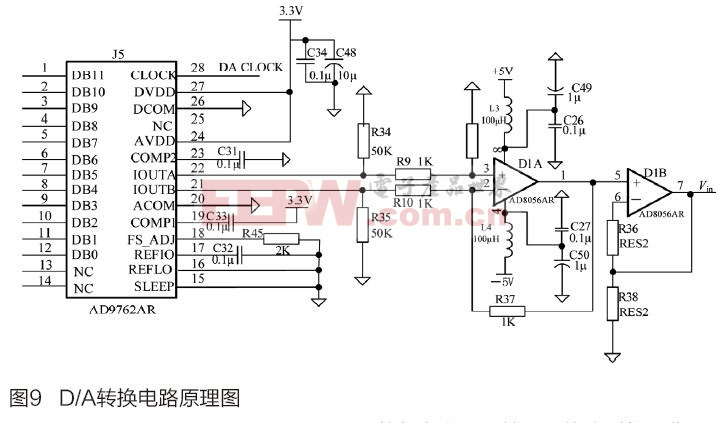

3.4 模数转换电路的设计

在波形数据产生以后,产生的数据通过D/A转换器,将数字信号变为模拟信号,本系统选用的数模转换器是AD公司的AD9762。AD9762是一种低功耗、12位、125Msps的高速、并行输出的模数转换器,其相对精度为±2LSB,AD9762可采用2.7V~5.5V电源工作。由于差分信号具有抑制共模增益的作用,信号特性更好,所以设计采用AD8056AR运算放大器实现了差分信号转单端的电压信号。具体电路如图9所示。

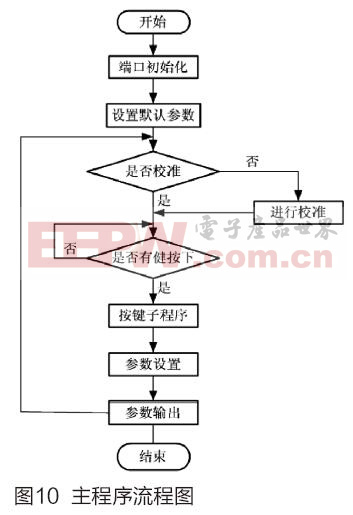

4 系统的软件设计

本系统初始化包括FPGA内核初始化、波形信号初始化,如正弦波,频率为1KHz初始值设定。系统初始化完成后通过软件对从芯片中读出的数据进行校准,校准完成后进入键盘扫描。当检测到有按键按下时,系统进入相应的子程序,其主程序流程图如图10所示。

5 实验结论

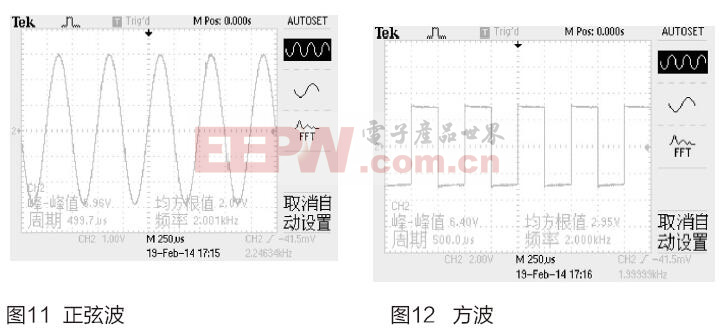

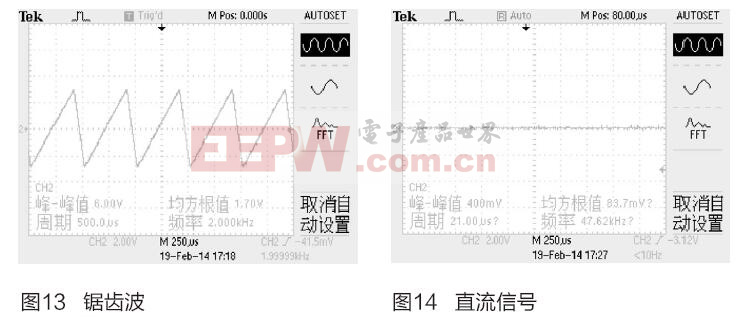

本系统研制的函数信号发生器可以实现双路同步数据输出,一路TTL电平输出,一路标准波形输出,包括正弦波、方波、锯齿波、直流电压信号。其中正弦波最大带宽10MHz,其它波形最大带宽100KHz,峰-峰值10.4V。本系统经计量所检定机构检测,检定结果如下。

1. 输出频率准确度,如表1所示。

2. 最大开路输出幅度(≥10Vpp):10.4V(峰峰值)。

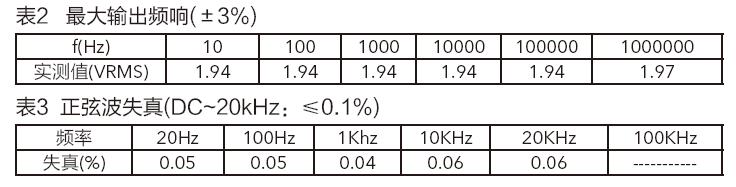

3. 输出最大频响,如表2所示。

4. 正弦波失真度,如表3所示。

5. TTL电平输出正常。

6. 上升时间/上冲(<100ns/2%):64ns/0%。

其中测试的波形信号符合标准,波形信号分别如图11正弦波、图12方波、图13锯齿波、图14直流电压所示。基于FPGA技术的DDS信号源,通过了检定机构验证,保证波形符合标准的基础上大胆采用一些新的设计思想,既缩短了开发周期,减小了电路板空间,又节省了成本。本文研制的这款信号源将为电路设计人员调试设备、测试电路带来极大的便利。

参考文献:

[1]王文华.基于DDS技术的任意波形发生器研究[D].浙江:浙江大学硕士学位论文,2002:1-4

[2]于鸿洲.基于DDS技术的函数波形发生器设计[D].黑龙江:哈尔滨工业大学硕士学位论文,2006:9-11

[3]李春明.数字波形合成技术理论研究与实践[D].黑龙江:哈尔滨工业大学博士学位论文,1995:19-35

[4]任丽军,童子权,赵爱明.双相信号发生器的设计[J].电测与仪表,2002,8:17-19

[5]蔡自兴.智能控制[M].北京:电子工业出版社,1990:35-43

[6]栾宝宽,方蕾,冯永浩.基于DDS的信号发生器的设计与实现[J].电子工程师,2005,31(10):38-3

[7]周俊峰.基于FPGA的直接数字频率合成器的设计和实现[J].电子技术,2005,5:43-45

[8]林建英,王涛,.基于DDS技术波形发生器的实验教学研究与实施[J].实验科学与技术,2006,4(1):75-78

[9]井新宇.基于CPU和FPGA/CPLD结构设计电子系统[J].电子工程师,2004,30(8):21-24

[10]童子权,任丽军,张礼勇.宽带信号调理电路的设计[J].哈尔滨理工大学学报,2000,3(5):71-74

[11]张福贵,姚振东.基于DDS的高性能信号发生器的实现[J].成都信息工程学院学报,2006,21(1):12-17

直接数字合成技术 FPGA 信号发生器 Quartus-II 201512 相关文章:

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)