直接数字合成技术实现函数信号发生器

芯片来设计,还可以采用FPGA芯片来设计,基本的设计方案简介如下。

2.1 采用高性能的DDS集成电路方案

随着微电子技术的飞速发展,目前高超性能优良的DDS产品不断推出,美国AD公司也相继推出了他们的DDS系列:AD9850、AD9851、可以实现线性调频的AD9852、两路正交输出的AD9854以及以DDS为核心的QPSK调制器AD9853、数字上变频器AD9856和AD9857。AD公司的DDS系列产品已具有较高的性价比,目前取得了极为广泛的应用。采用专用的DDS芯片AD9850来设计电路,其典型电路如图2所示。

优点:开发周期短,实现系统简单(最小系统+DDS芯片),系统后加模拟调理电路。

缺点:国外厂商的芯片的输出指标尽管很高,如有AD9852、AD9854,而且实现起来比较简单,只需送人按其指定的公式算出频率控制字即可输出波形,但存在着功能单一的缺点。

2.2 采用FPGA芯片的DDS方案

DDS技术的实现依赖于高速、高性能的数字器件。而FPGA芯片就具有速度高、规模大、可编程以及有强大EDA软件支持等特性,十分适合实现DDS技术。Altera公司的现场可编程逻辑阵列具有高性能、高集成度和高性价比的优点,此外它还提供了功能全面的开发工具和丰富的IP核、宏功能库等,因此Altera公司的产品在实现DDS技术方面获得了广泛的应用。通过FPGA技术则可以根据需要灵活地实现各种比较复杂的调频、调相和调幅功能,具有良好的实用性。针对生成波形信号质量而言,专用的DDS芯片采用特定的集成工艺,内部数字信号抖动很小,可以输出高质量的模拟信号,但控制功能单一固定;而FPGA也能输出较高质量的信号,而且输出信号灵活,虽然达不到专用DDS芯片的水平,但信号精度误差在允许范围之内。

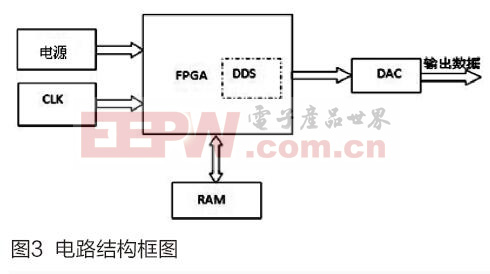

基于DDS技术原理选用的可编程逻辑器件、D/A转换模块、外部存储模块,通过数学函数式来生成波形信号,电路总体结构框图如图3所示。

优点:

(1)RAM查询表法结构比较简单,只需要在RAM中存放不同相位对应的幅度序列,然后根据相位累加器的输出对其寻址,经过D/A数模转换器和低通滤波器输出。

(2)硬件实现比较容易,可以实现任意波形的输出。

在基于DDS原理的基础上,利用可编程逻辑芯片设计的DDS硬件电路,同样可以达到专用的DDS芯片所产生的波形性能。因此本系统采用的方案技术是基于FPGA技术的DDS设计方案。

3 硬件电路的设计

本文提出的信号源将采用方案二实现,原理将通过直接数字合成的方式,逐点读出波形存储器中的波形数据,通过D/A转换器和低通滤波器后输出所需的波形,通过改变参考时钟的频率和计数步长就可以实现频率的改变,本系统的硬件结构框图如图3所示。

本文提出的基于FPGA技术的DDS信号源的技术方案,由于可编程逻辑器件以其速度高、规模大、可编程及有强大的EDA软件支持特性,十分适合实现DDS技术,所以本系统采用Altera公司的Cyclone IV型EP4CE6F17C8作为波形生成的核心部件,具体芯片功能的特点如下。

(1)低功耗、高性能,控制逻辑单元6272个,片内电压支持3.3V,2.5V,内核电压1.2V。

(2)支持多种下载方式,支持AS、AP、PS、FPP、JTAG。

(3)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

(4)FPGA采用高速CMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

3.1 电源电路的设计

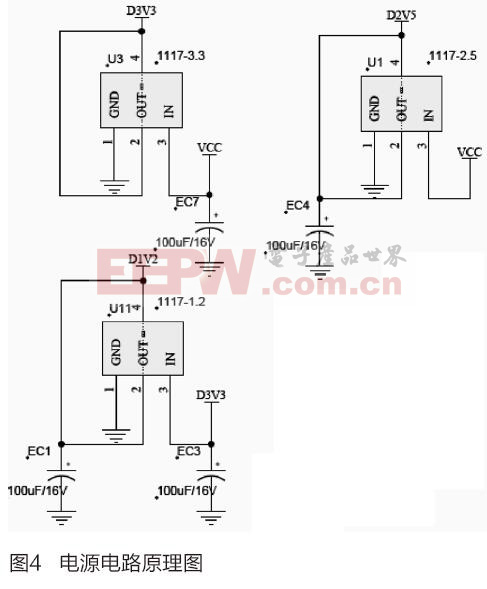

本系统采用的FPGA为Altera公司的Cyclone IV型EP4CE6F17C8,该芯片的片内电压支持3.3V,2.5V,1.2V,因此根据设计需要,使用线性稳压器件AMS1117系列分别产生相应的电源电压,供给本开发系统,该线性稳压芯片使用简单,纹波电压小,对系统的干扰也小,电源电路如图4所示。

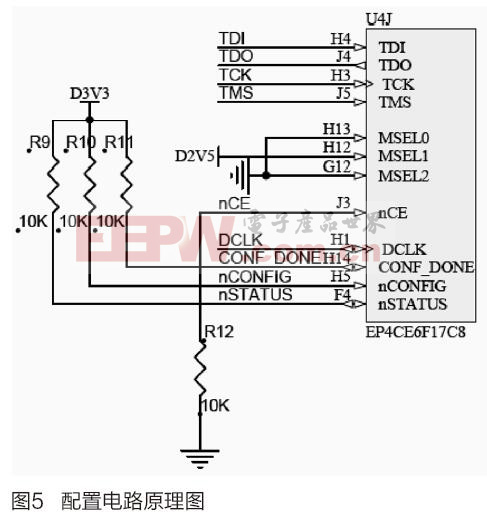

3.2 FPGA配置电路的设计

该款FPGA芯片支持5种下载方式,在本系统中采用JTAG下载方式,图5中的nCONFIG、nSTATUS和CONF_DONE则需要拉高,MSEL引脚不能悬空。其配置电路如图5所示。

3.3 波形生成电路的设计

波形生成电路是信号源的核心,也是DDS技术的集中体现。这部分电路主要通过EDA软件Quartus-II12.0对FPGA编程实现。通过对FPGA内部各种逻辑电路的设计实现输出多种波形、波形个数的控制、输出信号的门控等功能,具体模块框图如图6所示。

送数及保持模块负责接受来自CPU内核的相位步进增量,并按一定的时序保持或传送给相位累加器,相位累加器按时钟频率累加送来的相位步进量。由于要求每个周期采样点数不小于50个且信号频率达到1MHz,所以相位累加器的时钟频率需达到50MHz以上,时钟信号由锁相环通过倍频分频后提供。相位累加器的输出信号送到各波形生成电路,通过线路选择模块可选择其中一种波形输出送给后级选择电路,再通过线路选择模块选择普通模式、门控模式、计数模式其中的

直接数字合成技术 FPGA 信号发生器 Quartus-II 201512 相关文章:

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)