基于HMC833LP6GE的宽带本振源设计

摘要:为了实现宽带本振信号输出,本方案利用锁相环芯片HMC833LP6GE、数控衰减器HMC624LP4和滤波器组相结合,设计出一款高性能宽带本振源。经过实际测试,所有指标都达到了设计要求。

引言

宽带本振源是通信、雷达、仪器、空间电子设备等电子系统中的关键模块,其指标高低直接影响电子系统的性能。对于宽带本振源的设计,很多人做了深入的研究[1-2]。本文利用锁相环芯片HMC833LP6GE、数控衰减器HMC624LP4和滤波器组相结合,设计出一款宽带宽(400 MHz~6000 MHz)、低相噪(-100 dBc/Hz@10KHz)和高性能本振源。

1 方案设计

1.1 设计指标

频率范围:400 MHz~6000 MHz;

频率分辨率:3 Hz;

相位噪声:≤-90 dBc@1kHz,≤-100 dBc@10kHz;

输出功率范围:-2 dBm~2 dBm;

谐波抑制:≤-40 dBc;

杂散抑制:≤-60 dBc。

1.2 设计方案

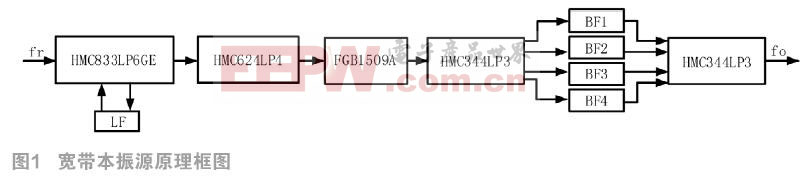

本设计方案原理框图如图1所示。利用Hittite公司(编者注:2014年被ADI收购)的一款宽带锁相环芯片HMC833LP6GE产生400 MHz~6000 MHz输出频率。HMC833LP6GE芯片内部集成了VCO,其基本频率是1500 MHz~3000 MHz,利用内部集成的分频器和倍频器可将输出频率扩展到25 MHz~6000 MHz[3],满足本方案的频率范围要求。利用Hittite公司的数控衰减器HMC624LP4和FIRSAR公司功率放大器FGB1509A对输出信号进行功率控制,使其满足 -2 dBm~2 dBm的输出功率要求。利用滤波器组对其谐波和杂散进行抑制,使本振源的输出信号满足谐波和杂散的要求。

2 关键电路设计

2.1 HMC833LP6GE电路设计

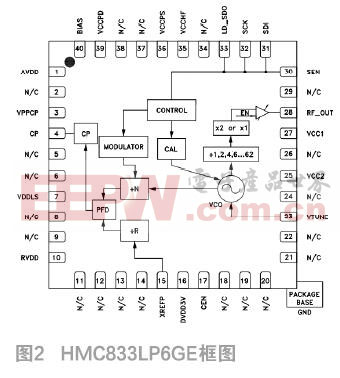

HMC833LP6GE芯片内部集成了鉴相器、电荷泵、VCO、调制器(包括19位的整数分频器和24位的小数分频器)、倍频器和分频器,如图2所示。

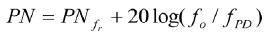

HMC833LP6GE的datasheet中给出它的归一化相位噪声是-227 dBc/Hz。在锁相环中,环路带宽以内的相位噪声由参考晶振和鉴相器噪声共同决定;环路带宽以外的相位噪声由VCO相位噪声决定。根据PLL相位噪声理论,环路带宽内的相位噪声与输出频率、鉴相频率以及噪声基底有关,具体噪声可以由公式(1)[4]表示:

![]() (1)

(1)

其中PDnoisefloor表示鉴相器归一化噪底,fPD表示鉴相频率,fo表示锁相环输出频率。

如果HMC833LP6GE的底噪对相位噪声的影响起主导作用,环路带宽内的相噪为:

![]()

如果参考信号的底噪对相位噪声的影响起主导作用,环路带宽内的相噪可以由公式(2)进行估算:

(2)

(2)

其中PNfr表示参考信号的相噪。

PN=-150+20log(6000/50)=-108.5dBc/Hz

根据估算,当选用HMC833LP6GE这种具有低噪底的锁相环芯片和频率为50 MHz、相噪为-150 dBc/Hz@10kHz的参考晶振时,估算的相位噪声完全能够满足设计指标。当参考频率为50 MHz,又因为调制器的小数分频器是24位,所以频率分辨率达2.98 Hz,满足频率分辨率是3Hz的要求。

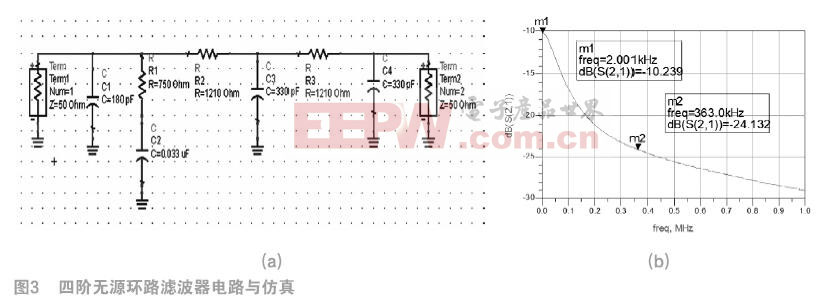

对于HMC833LP6GE的电路设计主要是设计环路滤波器,环路滤波器具有低通特性,可以起到低通滤波器的作用,更重要的是它对环路参数调整起着决定性的作用[5]。它决定了锁相环的杂散抑制、相位噪声、环路稳定性、锁定时间以及捷变时间等重要的环路参数。所以在所有频率合成器的设计中,环路滤波器的设计都是至关重要的,环路滤波器能够滤除鉴相器输出信号的高频分量和噪声。同时在含有电荷泵的锁相环中,环路滤波器还具有把电荷泵的电流转换成压控振荡器控制电压的作用。本设计利用ADS2009仿真软件设计了四阶无源环路滤波器,如图3所示。经过实际调试,相噪满足设计要求。

2.2 预稳幅电路设计

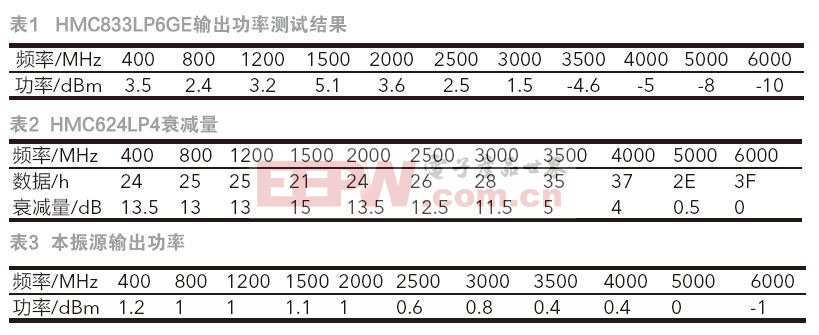

HMC833LP6GE输出功率测试值如表1所示。由实际测试结果可知,在400 MHz~6000 MHz频率范围内,HMC833LP6GE的最大功率是5.1dBm,最小功率是-10dBm,频率响应为15.1dB。而本方案的设计指标要求输出功率范围是 -2dBm~2dBm。为了满足方案要求,设计出一个预稳幅电路与HMC833LP6GE的输出端相连。预稳幅电路选用Hittite公司的电子数控衰减器HMC624LP4和FIRSAR公司的功率放大器FGB1509A组成。HMC624LP4有6位数字端控制,可通过FPGA送数,控制其衰减量,精度达0.5dB,衰减量为0 dB~31.5 dB[6]。FIRSAR公司的功率放大器FGB1509A使用频率范围是DC~9 GHz,在2 GHz时增益为15 dB。通过改变HMC624LP4的6位数字端控制的数据,并用频谱仪测试本振源输出端的功率,使其满足本方案输出功率范围-2 dBm~2 dBm的设计指标要求。HMC624LP4的频率、控制数据与衰减量的关系如表2所示。本振源输出功率测试结果如表3所示。通过预稳幅电路的设计,使本振源输出功满足方案要求。

2.3 滤波器组电路设计

由于HMC833LP6GE的基本频率是1500 MHz~3000 MHz,利用内部集成的分频器和倍频器将输出频率扩展到400 MHz~600

本振源 HMC833LP6GE 稳幅 滤波器组 201606 相关文章:

- 基于模糊PID控制器的网络控制系统仿真研究 (05-26)

- 现可使用60 GHz回程链路提升蜂窝容量(05-26)

- 高速移动条件下位同步器的设计(05-26)

- 多重文本水印算法在电力信息安全中的应用 (05-26)

- 基于Zigbee技术家用无线网络的构架(12-14)

- 无线通信领域中的模拟技术发展趋势(蜂窝基站)(09-22)