基于FPGA的高速数据传输研究

摘要:大数据发展如火如荼,解决串行数据高速传输已成当务之急。本文正是以此为出发点,介绍了Xilinx FPGA内嵌的高速串行收发器RocketIO。测试结果表明,RocketIO收发器的传输速度最高可达6.6Gbps,可以完全胜任各种高速数据的传输与处理。

引言

近年来,电子行业的发展走进了黄金时期,优势明显的串行传输无论在速度上还是信号完整性上都得到了飞速发展。无论高速AD采样后的数据接收,还是高速实时数据的传输与处理,都离不开高速串行总线。尤其对大型的采集系统,往往需要在单位时间里采集到成百上千个高精度的实时数据,这就要求在进行串行传输时速率达到百兆,甚至千兆每秒的级别。而Xilinx FPGA所提出的RocketIO 正是一种完全可以满足当前需求的解决方案。

本文主要介绍了RocketIO GTX的原理,并在此基础上提出设计中需要注意的设计要点,最后进行了板间高速数据传输的测试,给出了实时数据的采样波形图。

1 RocketIO GTX收发器介绍

RocketIO GTX是Xilinx公司FPGA内嵌的一种可配置的高速串行数据收发器,其传输速度在600Mbps~6.6Gbps[4]。该公司Virtex-5与Virtex-6系列FPGA都内嵌了RocketIO GTX,且其结构和工作原理也基本相同[1],本文将以Virtex-6 系列FPGA内嵌的GTX为重点进行介绍。

1.1 RocketIO GTX主要特点

● 每个通道收发器支持从600Mbps~6.6Gbps的全双工传输速率;

● 收发器内嵌发送时钟生成电路和接收时钟恢复电路;

● 差分输出端5级可配置电压(110mV~1130mV);

● 发送端支持可编程预加重/去加重,和判定反馈均衡(DFE);

● 支持可编程差分输出电压摆幅(110mv~1130mv)和可编程预加重;

● 收发器支持直接和交流耦合方式,可兼容多种高速接口标准;

● 片内集成可编程差分终端电阻;

● 支持片内多种环回测试模式;

● PCS集成多种可选编码功能,如comma字符对齐、8B/10B编码、时钟修正和通道绑定[2]。

1.2 RockerIO GTX内部结构

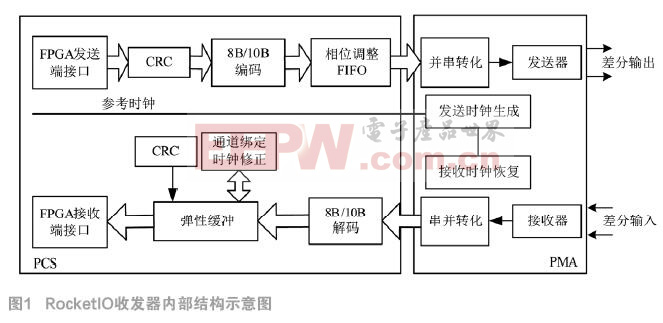

RocketIO GTX收发器由两部分组成:PCS(Physical Coding Sublayer)和PMA(Physical Media Attachment,物理媒介层),如图1所示。

其中 PMA部分主要包括串行和解串器、发送和接收驱动器、时钟产生和恢复单元;PCS 部分主要包括 8B/10B 编解码、通道绑定、时钟修正和 CRC校验模块。

● 8B/10B 编解码

8B/10B编码机制是进行高速串行传输时普遍采用的编码方式,其实现原理是将8位字符根据对应码表转化为10位字符,这种转换保证了通道的直流平衡性,有利于交直流耦合,提高信道传输质量。

● 通道绑定

通道绑定(Channel Bonding),一种通过一定协议将多个串行通道绑定达到并行传输,目的在于实现对数据吞吐率增大的技术。绑定原理是,在所有并列的串行通道中,定义一个主通道,其它均为从通道,主通道发送同步使能信号来与其它从通道进行对齐,从而解决各个通道数据同步问题,实现串行通道的并行绑定。

● 串行器和解串器

在发送端,收发器把输入GTX的参考时钟作20倍频,作为发送线路的参考时钟,然后将经过编码的并行数据转化为串行数据,从串行差分端发送出去;在接收端,时钟恢复电路从比特流中提取出时钟相位和频率,恢复出接收时钟,将串行数据解码并转化为并行数据,送入用户接口以进行其他操作。

● 时钟修正

时钟修正(Clock Correction)目的在于发送端与接收端的时钟匹配,在收发器的TX端,对要发送的串行数据中插入特定的修正序列,RX端通过这些修正序列提供的信息对时钟进行修正。

2 RocketIO GTX设计要点

要使RocketIO模块以最佳性能工作,实际设计中需要考虑到诸多设计因素,本节将对设计中经常遇到的问题进行讨论。

2.1 参考时钟

高速串行数据的传输中,为了实现高速,对时钟的要求当然就更为苛刻,这就要求用来驱动收发器的时钟必须具备高性能、低抖动的特点。一般来讲,GTX收发器提供了3种参考时钟的驱动方式:

①从外部GTX专用时钟端口输入来驱动时钟路由;

②从相邻Quard的专用时钟路由获取;

③从FPGA内部获取。

每个Quad中都拥有两个专用差分时钟输入MGTREFCLK0[P/N]和MGTREFCLK1[P/N],它们是时钟源的接口,为整个GTX的时钟提供保障。在设计中,当选用这种方式的时钟供应时,需要对原语IBUFDS_GTXE1进行例化。需将原语IBUFDS_GTXE1的输出做为GTXE1的端口MGTREFCLKTX[0]和MGTREFCLKRX[0]的输入。需要注意的是,即使在设计中未使用TX PLL,MGTREFCLKTX[0]仍然需要被连接[5]。单个外部参考时钟用法如图2所示。

前两种参考时钟的驱动方式都是使用GTX所集成的专用时钟路由,在精度上能得到很好的保障。第三种由内部全局时钟网络提供,会引入更大的抖动,而

高速串行 RocketIO 存储系统 201609 相关文章:

- 不同光纤收发器间(QSFP与GTH)通信研究与实现(07-28)

- 基于Zigbee技术家用无线网络的构架(12-14)

- 无线通信领域中的模拟技术发展趋势(蜂窝基站)(09-22)

- 新一代移动通信系统及无线传输关键技术(06-19)

- 蜂窝移动通信基站电磁辐射对人体影响的探讨(04-10)