不同光纤收发器间(QSFP与GTH)通信研究与实现

摘要:本文介绍了Xilinx Virtex-6 HXT系列FPGA内嵌光收发器GTH与Tyco Electronics光收发器QSFP,实现了光纤数据的高速传输。

引言

随着通信行业的迅猛发展,对数据吞吐量提出了更高的要求,铜互连开始向光纤互连转型,设计出符合高性能光纤抖动标准的收发器是转型成功的关键因素。

赛灵思公司(Xilinx)推出的Virtex-6 HXT系列的FPGA所内嵌的GTH收发器拥有领先的收发器抖动性能,为业界提供了较高的串行带宽,可实现与行业标准 SFP+、XFP 和 CFP等高速率光纤模块的无缝连接,满足新一代光纤传输应用的需求。泰科电子(Tyco Electronics)提供四通道小型可插拔QSFP(Quad Small Form-factor Pluggable)的光纤收发器,支持每通道速率高达 10Gbit/s 。本文主要介绍赛灵思公司内嵌的光纤收发器GTH与泰科电子的QSFP光纤收发器互连对接,实现光纤通信,并通过实验,给出最终结果和采样波形图。

1 GTH收发器设计要点

要达到GTH收发器的最佳性能,需要考虑到诸多设计因素,本文针对在设计过程中遇到的具体问题展开相关讨论。

1.1 参考时钟

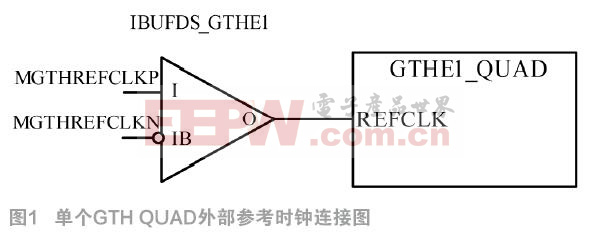

为了满足高速数据通信的需求,GTH收发器必须具备高性能、低抖动的参考时钟。GTH收发器参考时钟由REFCLK端口提供,其驱动方式有两种:由外部差分晶振直接驱动专用时钟路由和使用从相邻QUAD的专用时钟路由获取的时钟。使用专用时钟路由可以给GTH QUAD提供性能最佳的时钟,而通过专用的时钟引脚IBUFDS_GTHE1原语,可以直接驱动专用时钟路由,常采用外部高性能时钟输入经过专用引脚驱动输出参考时钟REFCLK,其时钟连接图如图1所示。

1.2 初始化及复位

GTH QUAD的复位有三种方式:上电配置FPGA自动完成复位、复位序列给GTHRESET和GTHINIT端口复位以及通过拉高POWERDOWN端口复位PCS逻辑。常用的复位方式为第一和第二种,第一种复位方式要求GTH QUAD必须有稳定的参考时钟和电源,若参考时钟在芯片配置后输入,则需第二种复位方式。表1给出了第二种复位方式需要的端口及说明。

1.3 用户时钟

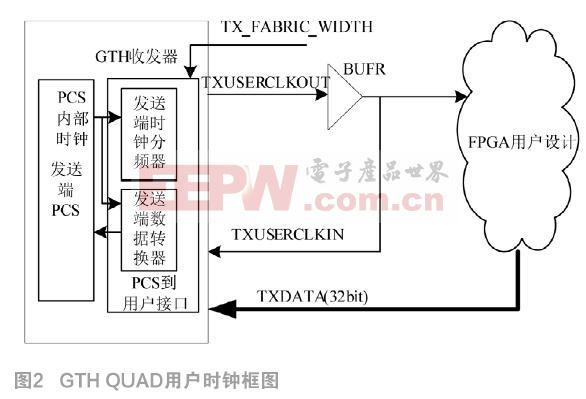

GTH收发器提供了发送端和接收端的并行用户时钟TXUSERCLKOUT和RXUSERCLKOUT,而在TXUSERCLKIN时钟发送并行数据到TXDATA端口时,在RXUSERCLKIN时钟上升沿接收的并行数据从RXDATA端口读出,输入用户时钟TXUSERCLKIN,RXUSERCLKIN为TXUSERCLKOUT和RXUSERCLKOUT经过缓冲BUFG驱动,两者不能来源于同一时钟。图2是发送端用户时钟框图,接收端用户时钟框图和发送端框图一样。

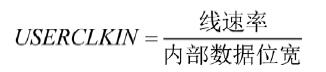

(1)

(1)

由公式(1)可知,线速率为5Gbps时,数据位宽32位经8B/10B编码后,发送端与接收端用户时钟USERCLKIN为125MHz。

1.4 接收端并行数据对齐控制

GTH收发器接收端并无对齐控制配置,需要外加FPGA逻辑实现接收数据对齐。接收端对齐控制原理是对接收端未对齐的并行数据检测Comma字符,若找到Comma字符对应位置,其后续位置的所有数据均已对齐。

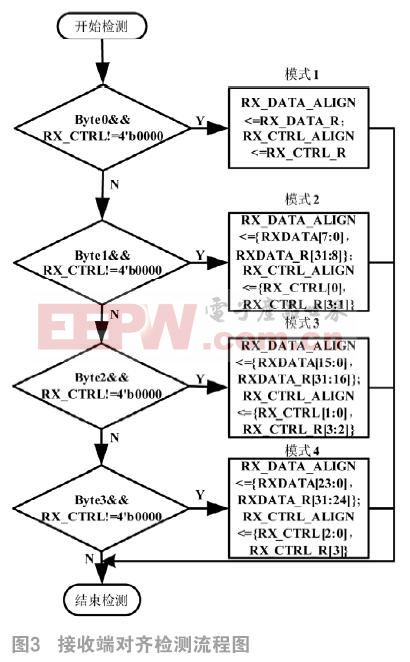

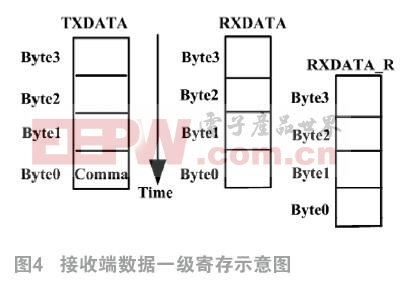

其程序流程图如图3所示。发送端并行数据为4 Bytes,发送Comma时,TXDATA[31:0]=32’h000000BC,对应设置TXCTRL[3:0]=3’b0001,接收端并行数据RXDATA的Comma字符可能出现的位置为Byte0、Byte1、Byte2和Byte3。当检测Comma字符出现在Byte0位置时,进入模式1操作,对接收端并行数据RXDATA进行一级寄存,对齐的数据即为一级寄存后的数据RXDATA_R,其示意图如图4所示;当出现在Byte1位置时,进入模式2操作,对齐的数据则为{RXDATA[7:0],RXDATA_R[31:8]};出现在Byte2位置时,进入模式3操作,对齐的并行数据为{RXDATA[15:0],RXDATA_R[31:16]};出现在Byte3位置时,进入模式4操作,对齐并行数据是{RXDATA[23:0],RXDATA_R[31:24]}。同时,为了便于后级处理,控制标志位RXCTRL也应该进行对齐操作,其原理和RXDATA一样,这里不再赘述。

2 光收发器模块QSFP架构和工作原理

为了实现多路光纤数据通信,这种小型化、低成本、低功耗、高速率及可热插拔的光收发模块是最佳选择。所采用的有源光缆组件包括屏蔽罩、有源光缆AOC(Active Optical Cable)、光收发模块QSFP和叠接式集成连接器。屏蔽罩用于抑制屏蔽罩至挡板与屏蔽罩至模块接口之间的EMI(Electromagnetic Interference,电磁干扰),表面贴装连接器能够提供良好的电气性能,符合包括接口与主板设计在内的SFF-8436工业标准要求。

发送部分集成了4通道VCSEL(Vertical Cavity Surface Emitting Laser,垂直表面腔发射激光器)阵列、4通道输入缓冲器、激光驱动器、控制模块和激光器偏置模块。发送端输入缓冲器提供了兼容CML(Current Mode Logic,电流模式逻辑)电平的高速串行接口,其数据传输速率一般在1Gbps至10Gbps之间,电压摆

Virtex-6 HXT FPGA 高速串行互连 GTH;QSFP 存储系统 201608 相关文章:

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)