不同光纤收发器间(QSFP与GTH)通信研究与实现

幅为200mV~800mV;控制接口集成了LVTTL电平的I2C总线及低速控制接口,用于数字诊断检测。接收部分集成了4通道的PIN光电二极管检测阵列、4通道TIA(Trans-impedence Amplifier,跨阻放大器)阵列、4通道输出缓冲器、控制模块和激光器偏置模块[4]。

其基本原理为:发送部分,4对差分串行数据经输入缓冲器缓冲,激光驱动器对调制电信号进行相应处理,随后输出,调制电流及偏置电流驱动VCSEL阵列,VCSEL阵列将电流信号转化成光信号,再由光接口输出。接收部分,PIN光电二极管阵列将从光接口输入的光信号转化成电流,4通道的跨阻放大器TIA放大转变为4路数字电压信号,经接收端的输出缓冲器,输出CML电平信号[5]。

3 互连系统分析

双端光收发模块的一端接至QSFP1插槽,另一端接至QSFP2插槽,可形成外环回,可实现4路光纤数据的高速传输。

4路光纤数据传输流程:GTH收发器GTH5~GTH8四路发送端发送并行数据源,输出串行传输速率为5Gbps的数据流经过QSFP2模块进行光电转换,光信号经光缆传输至另一端,再由QSFP1接收光信号,随后光电转换后输出至GTH1~GTH4收发器的接收端RX。由之前GTH设计要点可知,单通道GTH接收端完成串并转换后,数据位宽为32位,接收端用户时钟RXUSERCLKIN为125MHz,其单路数据传输速率为500MB/s。同理GTH1~GTH4发送端发送并行数据,通过光缆从GTH5~GTH8接收端接收数据。

4 实验结果和分析

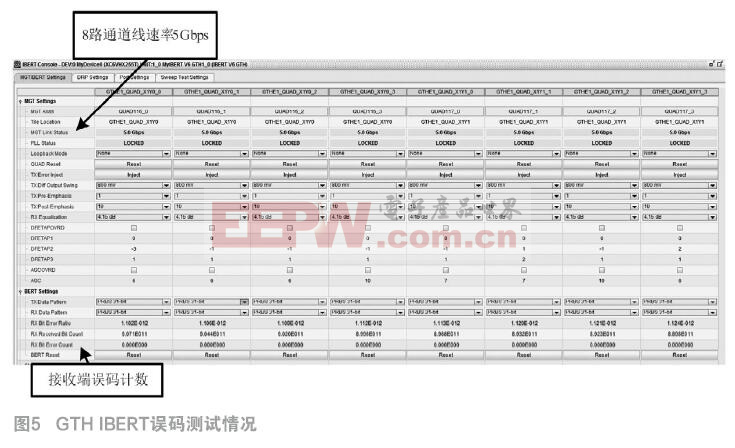

IBERT是集成式比特误码率测试仪,是Xilinx专门用于具有高速串行接口的FPGA芯片的调试和交互式配置工具[6],使用IBERT测试GTH收发器与光模块QSFP通信链路情况,配置MGT/IBERT选项,选取测试时间4800s,其测试结果如图5所示。

由图5可知,8路光纤链路线速率为5Gbps时,发送端数据设置为PRBS(伪随机二进制序列)数据类型,PRBS相当于“随机数据”,因此它的频谱特征(在有限频带内)和白噪声接近,故它很适合用于测试数字通信系统性能。环回模式Loopback Mode设置为None,表明GTH1~GTH4、光缆与GTH5~GTH8链路外环回,在测试期间接收端误码计数一直为0,且误码率在10-12量级,满足通信要求,表明光纤链路通信正常,因此设计满足4路光纤数据的可靠传输要求。

下面通过发送递增码测试光纤链路的通信质量,发送Comma字符TXDATA[31:0]=32’h000000BC,对应控制标志位设置TXCTRL[3:0]=3’b0001,有效数据以十六进制0000_0000、0001_0001、0002_0002......格式递增,对应标志位设置TXCTRL[3:0]=3’b0000,以1024个同步字符和4096个有效数据为一包数据形式发送。图6为使用Chipscore Pro工具采集到的数据错位图,这种情况由于最初设计GTH接收端并没外加对齐控制,这里测试的为GTH QUAD116和QUAD117的第一通道收发情况,由图中的接收端控制标志端口rxtrl[3:0]=4’b0100,接收端并行数据端口gth_data_receive[31:0]=32’h00BC0000,可以看出数据发生错位,实际测试数据错位是随机的。所以接收端的对齐控制相当重要,是GTH收发器正确数据传输的关键。

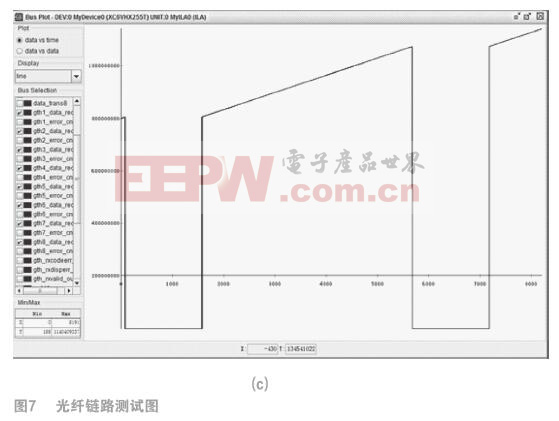

图7(a)为加入接收端对齐控制后采集到的接收正确图,GTH1~GTH4发送端发送递增码数据,通过光模块QSFP,GTH5~GTH8接收端接收到数据;(b)为GTH5~GTH8发送端发送递增码数据,通过光模块QSFP,GTH1~GTH4接收端接收数据;(c)为Plot工具画出的各路接收数据图。由图中的8路接收端通道的误码计数信号error_cnt=0及Plot曲线平滑无毛刺,可看出此链路传输数据正确,接收端无误码。

5 结束语

本文介绍了Xilinx公司Virtex-6 HXT系列FPGA集成的GTH收发器及光收发模块QSFP的原理,并对其互连系统进行设计与实现。可以看出,利用GTH收发器可与光收发模块QSFP无缝连接,并实现了4路光纤数据的对发对收。本系统可作为高速大容量存储阵列的前端,它满足了对光纤数据快速高效传输及暂存,具有很好的工程应用前景。

参考文献:

[1]田耕,徐文波. Xilinx FPGA开发实用教程[M]. 北京:清华大学出版社,2012.

[2] Xilinx. Virtex-6 Family Overview[M]. USA:Xilinx, 2012.

[3]Xilinx. Virtex-6 FPGA GTH Transceivers User Guide[M]. USA:Xilinx,2011.

[4]SFF Committee. SFF-8436 Specification for QSFP+ 10Gbps 4X PLUGGABLE TRANSCEIVER Rev4.8[S].USA,2013.10.

[5]王婷婷. QSFP光模块的技术与测试研究[J].信息通信.2015.5(149):33~35.

[6]徐妍,马丽珍,张丽. IBERT在FPGA中的应用[J]. 电子科技,2012,25(7):103-105.

本文来源于中国科技核心期刊《电子产品世界》2016年第7期第61页,欢迎您写论文时引用,并注明出处。

Virtex-6 HXT FPGA 高速串行互连 GTH;QSFP 存储系统 201608 相关文章:

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)