基于FPGA的高速数据传输研究

且驱动能力也有限,因此要尽量避免使用。

2.2 用户时钟

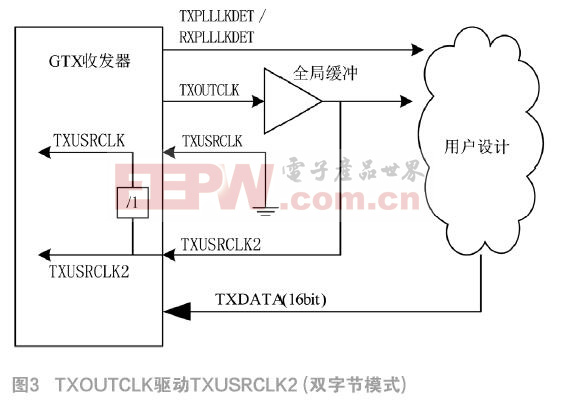

GTX的接收端和发送端都有两个用户时钟,这里以发送端为例进行介绍。这两个时钟分别为:TXUSRCLK和TXUSRCLK2。其中TXUSRCLK2是发送端TX的用户时钟,允许用户直接使用,由GTX的内部时钟TXOUTCLK驱动。用户将并行数据传输到发送接口,在用户时钟上升沿被采样并送入发送缓冲,经过编码以及串行化之后发送出去。TXUSRCLK是PCS内部逻辑时钟,不允许用户直接使用,其大小取决于如下公式[3]:

![]()

由于在设计中通常会选择8B/10B编码,因此16bit并行数据经过编码后变为20bit。这里需要注意的是,需要设置属性GEN_TXUSRCLK=TRUE。此时,TXUSRCLK端口必须拉低,逻辑时钟TXUSRCLK由GTX内部提供,并且用户时钟TXUSRCLK2大小与TXUSRCLK相同[4]。当设计中线速率选为3Gbps,可知用户时钟TXUSRCLK应为150MHz。时钟结构如图3所示。

GTX的接收端RX与TX基本相似,也包括两个用户时钟分别为:RXUSRCLK和RXUSRCLK2。其中,RXUSRCLK2是GTX接收端的用户时钟,由恢复时钟RXRECCLK驱动。RXUSRCLK的驱动方式和属性设置与发送端一致[5]。

2.3 Comma 检测对齐

Comma检测对齐模块是高速数据传输中必不可少的重要模块,高速数据的识别对齐是传输中的核心问题。在RX接收模块中,串行数据转换为并行前,必须经过边界字符对齐才能对所传输的数据进行识别,才能有后续的并行数据。在实现高速串行信号发送时,TX端会先发送comma字符,然后再发送数据。对应的RX接收端通过comma探测,当检测到comma字符后,需要进行对齐,然后接收数据[6]。

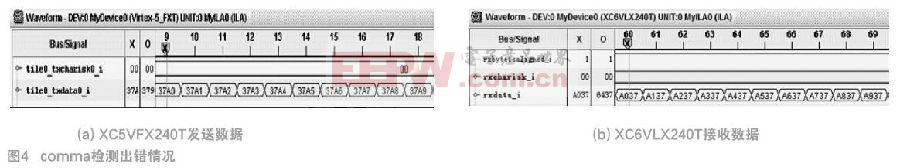

GTX收发器的comma模块在实际解码应用中通常选K28.1、K28.5和K28.7为comma字符,具体根据项目需求来选择。设计中,为了确保数据的对齐,通常会选择发送2000个左右的同步字符。在TX端发送K字符时,赋值TXCHARISK=2’b01,TXDATA=16’h43BC。这里TXCHARISK=2’b11表明对应数据的低字节为K字符,对应比特流中的comma字符。需要注意的是,当TXCHARISK=2’b11,发送TXDATA=16’hBCBC时,由于TXDATA中高八位和低八位相同,这样在接收端容易出现错位8位的情况。如图4所示。

造成这种情况的原因是,在进行K字符探测对齐的过程中,将两个K字符的低字节和下一个的高字节组合,这样探测对齐系统会认为实现了对齐过程,在接下来的数据接收过程中会以这种方式进行对齐。

3 应用系统

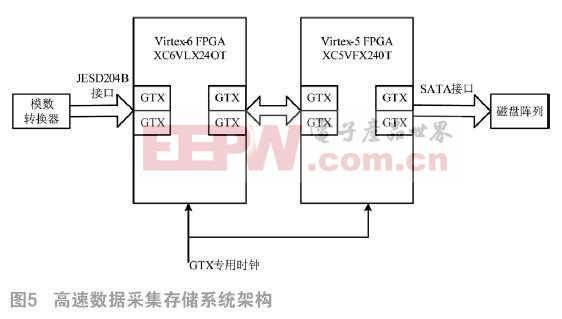

基于RcoketIO GTX的高速串行传输,设计出了一个高速数据采集存储系统,采集端使用XC6VLX240T,存储端使用XC5VFX240T。由图5可以看出,ADC的高速数据是通过其自带JESD204B接口与V6实现GTX互联的,V6与V5两FPGA间的数据传输也采用GTX传输,后面SATA设计中还是使用GTX来实现的。

从数据流来看,AD将采集的高速数据通过GTX(配置成JESD204B接口)送入Virtex-6,经过一定的数据处理后通过GTX发送至Virtex-5 FPGA,最终通过GTX(配置成SATA接口)存入磁盘阵列。由此可见,RocketIO GTX是整个系统中高速数据传输的核心。

4 实验结果和分析

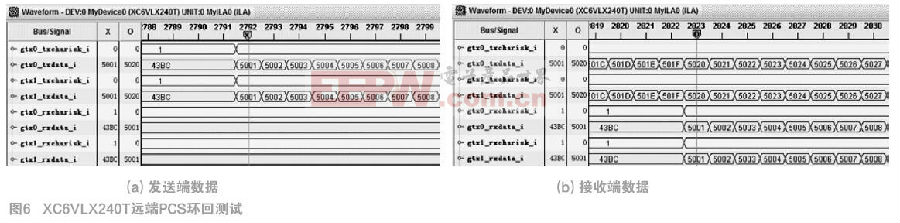

通常对系统设计中GTX通路的连接需要进行测试,以下将通过本V6端的PCS远端测试来验证其工作性能,也就是V6端发送测试数据至V5然后通过PCS环回至V6接收端,来看数据的正确与否。chipscope采样如图6所示。

由于远端PCS环回模式可以同时测试两端GTX的通信情况,故由图6可知,XC6VLX240T、XC5VFX240T可以正常通信。

高速数据传输中,经常要对数据进行各种转换,而数据的拼接与拆分是最常用的手段,图7是对一路 0000-FFFF的递增码,将递增码拆分成两路分别为4K数据和43BC。也就是将一个递增码分成TRIG1和TRIG2的两路GTX数据进行发送来测试数据的正确性。

由数据总线图可以看出,两路数据成完美递增状态。

5 结束语

本文以高速数据传输为出发点,介绍了基于RocketIO GTX 的解决方案,并给出了以GTX为核心的应用系统设计。由此可见,采用 RocketIO收发器进行高速串行数据的传输,在保证速度的前提下,传输过程中的信号完整性也得到了极大的保障,为高速数据的传输提供速度和质量上的保证 。

参考文献:

[1]Xilinx. Virtex-6 Family Overview[M]. USA:Xilinx, 2012.

[2]Xilinx. Virtex-6 FPGA GTX Transceivers User Guide[M]. USA:Xilinx,2011.

[3]李大鹏,陈长胜,王世奎等.基于FPGA的高速串行传输接口研究与实现[J]. 航空计算技术,2008,38(2):100-103.

[4] Abhijit Athavale,Carl Christensen.High-Speed Serial I/O Made Simple[J].USA:Xilinx

Corporation.2005.4.

[5]徐文波,田耘.Xilinx FPGA 开发使用教程[M].北京:清华大学出版社,2012.7. [4] Xilinx.

高速串行 RocketIO 存储系统 201609 相关文章:

- 不同光纤收发器间(QSFP与GTH)通信研究与实现(07-28)

- 基于Zigbee技术家用无线网络的构架(12-14)

- 无线通信领域中的模拟技术发展趋势(蜂窝基站)(09-22)

- 新一代移动通信系统及无线传输关键技术(06-19)

- 蜂窝移动通信基站电磁辐射对人体影响的探讨(04-10)