基于FPGA的TS流的UDP封装实现

摘要:为实现数字广播接收机输出的传输(TS)流方便地接入嵌入式平台,实现综合业务接收,本文基于现场可编程门阵列(FPGA),实现了将集成DVB-T(Digital Video Broadcasting-Terrestrial)高频头输出的TS流转化为UDP协议的IP流,进一步通过以太网接口进入嵌入式平台,支持综合业务接收。该接口转化模块借助FPGA,将缓存的TS流进行有效封装,设置以太网接口,输出UDP格式的IP流。实测表明,该接口转换模块可实现TS流到IP流的转换,支持嵌入式平台视频播放与综合业务接收。

引言

在互联网高速发展以及三网融合的趋势逐步推进的背景下,地面数字电视广播与互联网的融合得到了研究人员越来越多的重视。地面数字电视广播[1]音视频数据的传输流是编码格式为MPEG-2(Moving Picture Experts Group-2)的TS(Transport Stream)流。因此,传统广播接收机多输出TS流。

为支持嵌入式平台实现TS流传输的综合业务接收,本文在前期实现的数字广播接收机的基础上[2],采用FPGA作为转接,实现了TS流到IP流的封装,从而可以方便地将TS流接入嵌入式平台,实现利用嵌入式平台的基于TS流的综合业务接收。

1 硬件系统结构

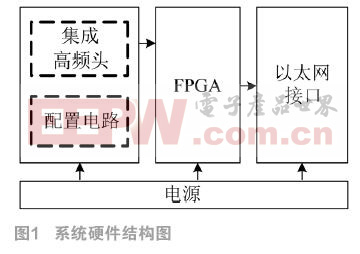

硬件系统主要包括电源部分、集成高频头[3]及其配置电路部分、FPGA部分和以太网接口输出部分。其工作原理如下:系统启动之后,由配置电路中单片机首先对集成高频头进行配置,然后FPGA等待接收由集成高频头输出的数据,接收的数据经过格式封装后,经以太网接口模块以UDP格式[4]的IP流输出。输出的负载数据为MPEG-2标准的TS包,可以在任何支持该标准解码的终端进行实时播放。

系统的硬件结构如图1所示,系统实现的是以FPGA为控制核心的接收、处理和转发系统,下面介绍每个部分的具体实现。

(1)电源部分

电源部分采用TI公司的LP3906电源管理芯片,该电源芯片被广泛应用于低功耗FPGA、嵌入式微处理器、DSP等系统的电源管理。其性能优秀,最高输出效率为96%,最大输出电流为1.5A。该芯片的输入电压为5V直流,由外部电源适配器提供。

(2)集成高频头及其配置电路部分

本部分电路由集成高频头以及其配置电路组成。集成高频头采用夏普公司的VA4M1EE6159。该器件功能是将天线接收到的DVB-T标准信号变频为中频信号[5],通过解调、基带处理和打包,最终输出TS(Transport Stream)流[6]。TS流输出有两种常用接口,分别是异步串行接口(ASI,Asynchronous Serial Interface)和同步并行接口(SPI,Synchronous Parallel Interface),VA4M1EE6159采用同步并行接口,该接口共有11位信号线,包括3位控制信号线和8位数据信号线。3位控制信号分别为时钟信号MCL、同步信号SYN和数据有效信号VALID。其中,集成高频头的时钟信号MCL输出为9MHz。SPI接口使用同步控制信号,所以传输速率由实际情况决定。

配置电路采用Silicon Lab公司的C8051F120单片机作为集成高频头的配置电路控制器。该款单片机兼容8051单片机的指令集,速度是普通8051单片机的数十倍,外部无源晶振为25MHz,最高速度可达100MIPS(百万指令集每秒),支持JTAG(Joint Test Action Group)调试接口。该单片机具有较高处理速度,对于实现严格时序有很大的优势。

(3)FPGA部分

FPGA部分由FPGA电路及其配置电路组成。FPGA采用的是Xilinx公司的Spartan-3系列XC3S700A芯片。该芯片最大用户I/O数量为372,具有分布式RAM为92kb、块RAM为360kb,拥有8个数字时钟管理单元(DCM,Digital Clock Manager),slice数量为5888。配置模式为JTAG模式和主串(Active Serial)模式。采用的存储芯片是XCF04S,存储空间为4M,外部为50MHz无源晶振。

FPGA是系统的控制和计算核心[7],负责接收集成高频头的TS流数据,将接收的数据缓存、计算、打包,并驱动DM9000AEP芯片,将处理完成的数据以IP数据报的形式输出。FPGA芯片使用11个通用I/O与集成高频头相连,模拟SPI接口时序接收数据。作为DM9000AEP的驱动源,FPGA的物理管脚与DM9000AEP连接,用于按其控制时序驱动芯片工作。

(4)以太网输出部分

以太网输出部分使用的是10M/100M自适应的MAC层接口芯片DM9000AEP。该芯片是支持物理层自协商,支持IEEE802.3u全双工流量控制的快速以太网接口控制器。输出物理接口与RJ45相连。该以太网控制器使用的是25MHz的无源晶振,外部电路简洁。

DM9000AEP拥有4K双字大小的SRAM块,可以作为以太网帧结构的缓存。由于以太网帧结构最大为1500字节,所以可以缓存多个相同的帧结构。DM9000AEP有两个方面的功能。首先是完成与后级网络设备的物理层协商,建立链路;其次是接收FPGA的指令,执行指令、发送已经存

FPGA DVB-T TS流转IP流 201608 相关文章:

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)