基于FPGA的TS流的UDP封装实现

在于缓存中的以太网帧以及完成相关链路层功能。

系统硬件电路由LP3906模块提供统一的电源管理。集成高频头在配置电路完成配置之后,与天线相连,从天线接收DVB-T信号并将信号解调处理,以SPI接口输出TS流,是整个系统的数据源。FPGA是系统中枢,它模拟SPI时序接收TS流数据并打包为UDP格式,控制DM9000AEP以IP流输出。DM9000AEP完成与接收者的物理链路建立及辅助的链路层功能。

2 基于FPGA的封装转发实现

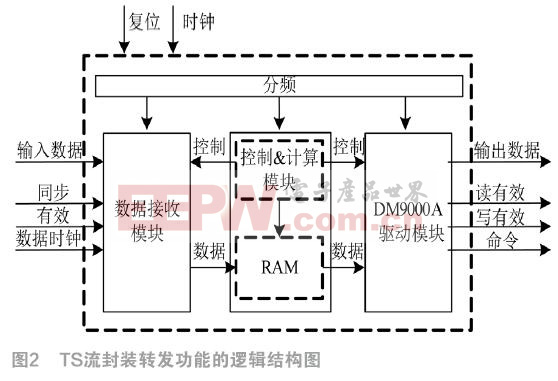

在系统实现过程中,TS流的接收、处理和转发部分都在FPGA内部实现。图2为FPGA实现的封装转发功能的逻辑结构图。主体由数据接收模块、控制计算模块和DM9000AEP驱动模块三个模块组成。数据接收模块模拟SPI接口时序接收集成高频头的输出数据;控制计算模块负责将接收的数据有序地存入RAM,并将RAM中的数据打包为IP格式;DM9000AEP驱动模块将IP格式的数据通过网口输出。

2.1 数据接收模块

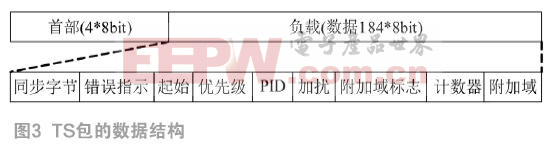

数据接收模块的功能是模拟SPI接口时序接收由集成高频头输出的TS流格式的数据。集成高频头数据输出宽度为8bit,接口时钟频率为9MHz。当有数据输出时,有效信号变为高电平。输出的TS流数据包含有4字节的首部和184字节的数据,总计大小为188字节,数据格式如图3所示。

TS流数据输出为突发模式,即在一个周期内只有小部分时间有数据输出,大部分时间没有数据输出。突发瞬时速率最高可达到72Mbps,这里的72Mbps为裸数据,增加数据头部等,最高瞬时速率将会增加到80~85Mbps之间。DM9000AEP的理论最高速率为100Mbps。由于在DM9000AEP的驱动中有额外开销,数据很难做到最大带宽。所以使用FIFO作为缓冲来匹配前后两者的速率差,既可以防止数据丢失,也方便进行数据处理。当FIFO中的TS流数据包的数量超过阈值时,则读有效信号为高电平,数据线输出数据。本部分电路实现的结构图如图4所示。

2.2 控制计算模块

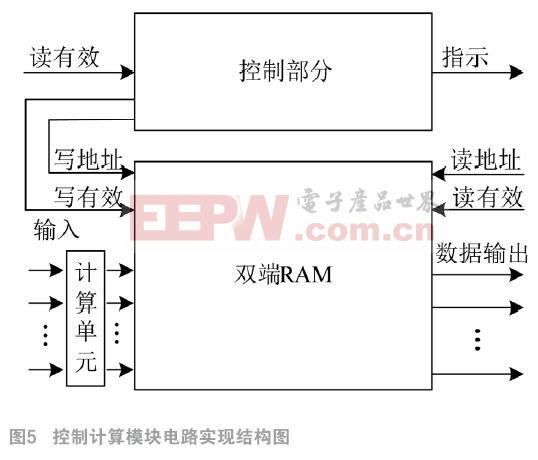

控制计算模块由控制部分、计算部分和双端RAM部分组成。本部分电路实现的结构图如图5所示。

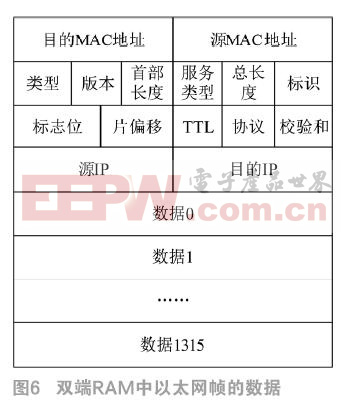

其中,双端RAM内存储一个完整的以太网帧,RAM中不同部分的功能如图6。源MAC地址设置为本机地址,目的MAC地址为广播地址,类型为IP数据报。IP数据报中版本、首部长度、服务类型、标志位、片偏移、TTL、协议、源IP以及目的IP为常量。其中,源IP设置为本机IP,目的IP为广播地址,TTL为64。以太网帧的数据大小范围是46~1500字节。为了最大限度地提高传输效率,取7个TS包作为一个以太网帧的数据部分,即1316字节。

以太网帧中数据段、标识字段和校验字段为变量。数据段由传输的TS流数据决定;标识字段为依次递增;校验字段则是将字段本身置为零之后,对IP数据报中每16比特进行二进制反码求和,将结果存入校验字段。这部分运算在计算部分实现。

控制部分时刻监视读有效信号的状态变化。当发现信号状态变化为有效,则接收前级模块的输出数据,并且按地址存入RAM。与此同时,在数据输入路径上的计算模块对数据进行反码求和运算,得到校验字段,并且进行递增运算,得到标识字段。计算完成后,两个字段分别按地址存入RAM中。此时,RAM中是一个完整的以太网帧结构。控制部分将会给出指示信号,通知DM9000AEP驱动模块可以读取UDP帧数据。

2.3 DM9000AEP驱动模块

DM9000AEP驱动模块通过状态机实现,负责对DM9000AEP芯片进行初始化及功能驱动。

DM9000AEP的初始化过程首先进行物理层(PHY)上电。物理层上电第一步是对DM9000AEP芯片内部的GPR寄存器清零,然后最低位赋值为1。在对物理层上电之后,延时应该超过2ms,最佳为5ms。第二步是将NCR寄存器进行两次软件复位,两次软件复位的目的是确保软件复位成功。每次软件复位延时30μs,正常的时间间隔是20μs左右。然后依次按着时序对NSR、ISR、TCR、BPTR、FCTR、SMCR的寄存器和物理地址进行设置。为了确保数据的通用性,物理地址设为广播地址。寄存器设置成功表示DM9000AEP初始化完成。

初始化完成后的DM9000AEP在检测到控制计算模块的指示信号变化后,在双端RAM的右端进行读取,将RAM中的一个以太网帧数据写入DM9000AEP的buffer中,并查询标志位,直到标志位变化表示发送完成。由于DM9000AEP的发送速度大于集成高频头的数据平均输出速率,所以不会出现双端RAM中数据被重复写的情况。

FPGA部分的三个模块采用的是流式的处理过程。数据接收模块模拟接口时序接收集成高频头的输出数据,是整个FPGA逻辑的数据源。控制计算部分负责对IP数据报进行计算打包,并且将完整的以太网帧存入双端RAM,完成之后通知驱动部分。DM9000AEP的驱动部分负责按时序初始化DM9000AEP,并在得到控制计算模块的通知

FPGA DVB-T TS流转IP流 201608 相关文章:

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)