逐次比较式ADC 采样频率的选取及应用

摘要: 在设计数据采集系统时, 一项重要的任务是选择模数转换器(ADC) 的采样频率L 根据采样理论, 采样频率至少应为输入信号带宽的两倍, 实际往往采用更高的采样频率来保证数据采集系统的精度L 但当逐次比较式ADC 的采样频率过高时, 会使其内部采样保持的开关电容充电不充分, 从而导致ADC 转换误差过大L选择一个合适的采样频率是保证数据采集系统可靠工作的关键L通过建立ADC 及前向通道的等效模型及推导, 在保证ADC 的转换精度下, 推出ADC 的采样时间与信号放大电路输出阻抗的匹配关系, 得到ADC 最合适的采样频率。

关键词:逐次比较式;模数转换器;开关电容;采样时间;转换精度

引 言

数据采集系统的前向通道一般是由三部分组成的: 传感器, 信号放大电路和模数转换器(ADC) 。 逐次比较式的模数转换器是试验机控制系统的数据采集模块及其它工业数据采集系统常采用的模数转换器L在设计这类数据采集系统时, 一项重要的任务是选择模数转换器(ADC) 的采样频率。 根据采样理论, 信号的采样频率至少应为输入信号带宽的两倍,实际往往采用更高的采样频率来保证数据采集系统的精度。 但当逐次比较式ADC 的采样频率过高时,会导致ADC 转换误差过大。这是因为这类ADC 的采样保持部分是采用开关电容阵列的结构。 这种结构是靠信号放大电路的输出电压对其内部的开关电容阵列进行充电, 即ADC 的采样阶段。 然后对电容阵列的电压值进行保持及转换得到对应的数字量L而对开关电容阵列进行充电需要一定时间, 如果ADC 的采样时间过短, 会导致ADC 内部的开关电容阵列并未完全充电, 即此时ADC 采得电压值低于实际电压值。 从而导致后面转换结果与实际误差过大而无效。 因此采样时间必须能保证开关电容阵列的充分充电, 才能保证采样值的精度。而开关电容阵列的充电时间取决于信号放大电路的输出电阻和ADC 的转换位数。 本文推导出ADC 的采样时间与信号放大电路输出阻抗的匹配关系, 在保证ADC的转换精度下, 得到不同转换位数ADC 的最佳采样频率。

模拟输入电路的分析

测控系统的传感器和信号放大电路经常采用差动式放大器和运算放大器变换电路等组成, 根据戴维南原理(Thven in’s theo rem ) , 可将其简化成一个放大后的等效电压信号源。 而逐次比较式ADC 的开关电容阵列结构, 在其采样期间, 等效于一个等效电容通过一个等效内部电阻与信号源相连L因此整个前向通道可等效并简化为图1。 图1 的等效电路对本文所分析T i 公司的TLC54X, TLC154X 和TLC254X 系列的逐次比1 较式ADC 都是有效的。

由于对图1 中ADC 的等效电容C i 的充电是呈指数变化, 见图2根据理论分析, 充电时间越长, 其上的电压U c 只是无限接近于等效信号源的电压U s为保持一定采样频率, 在以下的分析中, 假定当等效电容C i 上的电压值达到了1/16 L SB 的误差范围之内, 即算其进行了完全充电L因为在此采样误差下,再把其它的内部误差, 如DNL 和NL 一起统计进来, 可把总共的转换误差控制在 1/2 L SB 之内。

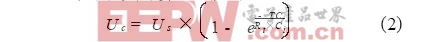

以图1 的等效电路为例, 在开关电容的充电时间内, 从0 V 到等效信号源的电压值, 并在1/16L SB 误差范围L其计算公式如下:

式中:U c 为等效电容上的采样电压;U s 为等效信号源的电压; R t 为R s + R i; R s 为等效信号源的输出电阻; R i 为ADC 的等效内部电阻; T C 为等效电容的充电时间。

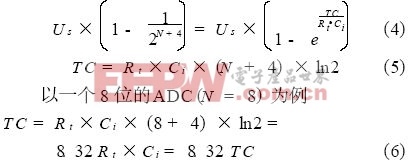

等效电容在1?16 L SB 误差范围内的的电压为

其中N 为ADC 转换精度的位数

将式(2) 代入式(3) , 得

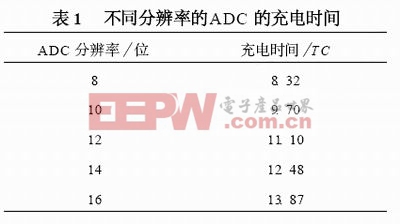

其中时间常数T C = R t C i因此一个8 位ADC 中开关电容的充电时间为8。 32 倍的时间常数。表1将显示各种位数的ADC 的充电时间。由上述计算过程可知,ADC 输入采样时间(T s)必须大于或等于其等效开关电容充电的时间常数,方可保证ADC 采样值不超过1/16 的L SB 的误差。

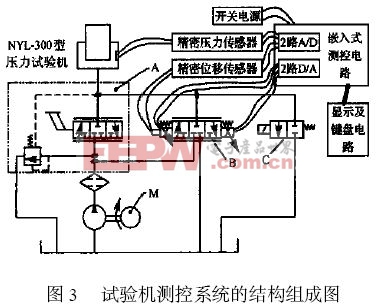

在试验机测控系统中采样时间的计算及比较

为了验证上述等效模型的有效性, 本文选用试验机测控系统等速加载来试验, 见图3。系统中的ADC 为TLC2543, TLC2543 是12 位精度SP I 接口的串行ADCL由TLC2543 数据手册可知, 其前8个I/O clock 为采样时间。在第12 个I/O clock 的下降沿开始AD 转换。因此其采样时间为

其中f I/O 为TLC2543 的I/O clock 频率。

由表1 知12 位的TLC2543 的充电时间及公式(5)。

在Ci = 100 (pF) 及R i = 1 (kΩ) 时, 另测得信号放大电路的输出R s = 2 1 (kΩ)

为保证TLC2543 的采样误差在1/16 L SB 之内, 单片机提供给TLC2543 的f I/O 不应高于2。 325MHz。当单片机提供给TLC2543 的f I/O 分别

采样频率 逐次 比较式 等效模型 时间常数 等效电路 ADCL 模拟输入 下降沿 开关电容 相关文章:

- FPGA工程师应如何挑选ADC和DAC(06-18)

- 解析在PCB设计中采用时间交替超高速模数转换器(01-21)

- 什么是逐次比较型ADC(模数转换器)(01-24)

- 精密逐次逼近型ADC基准电压源设计(03-30)

- ADI实验室电路:16位、100kSPS逐次逼近型ADC系统(02-12)

- 逐次逼近型ADC:确保首次转换有效(02-25)