利用SmartCompile和赛灵思的设计工具进行设计保存

口最优化来解决一个关键路径或包装问题, 那么,应该从设计中把那个Partition消除。在Partition接口上创建寄存器将排除出现时序或包装问题的可能性。

XST和Synplify Pro两者都可被用详细说明RTL Partitions。

在Partition流程中使用XST

如图4所示,要采用XST综合工具在ISE Project Navigator中创建Partitions,右击Sources列表中的实例并选择New Partition。从这个菜单可以修改其它的Partition属性,如保存。

在tcl接口中创建Partition,要使用这条命令:

% partition new

Partitions不能用批处理命令创建,因为他们需要在设计中的特定逻辑模块上设置一种属性。

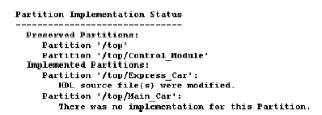

实现FPGA设计(XST, ngdbuild, map, par)的个别应用生成关于哪一个Partitions在它们各自的报告文件中被保存和实现的信息。例如,在这个XST 综合报告中,一些Partitions被保存,而其它的被重新实现。每一个已实现的Partition都有一个原因解释它为什么没有被保存。

在9.1i版本ISE中,对时序约束或命令行变更做出的修改—如努力级别—将迫使所有的Partitions被重新实现。

在Partition流程中采用Synplify Pro

在Synplify Pro Partition流程的情况下,用户在运行综合之前,指定RTL模块/子模块(Partitions)作为Synplify Pro中的编译点。在整个设计中运行最初的布局和布线之后,该工具检测哪些模块/子模块已经发生了改变,并且能利用这一变化对所选择的任意模块执行后续的增量布局和布线,与此同时,使其它已布局/布线的模块保持不动。在已传递到布局和布线的tcl文件中,有可能详细说明布局或布局和布线是否被保存(缺省是布局和布线)。

Synplify把时间戳写入到EDIF,它可用于确定每一个编辑点自上一次的布局和布线运行后是否发生改变。一份tcl文件也由Synplify 写入,从而为赛灵思布局和布线定义分区。当用户指定“syn_hier=locked,physical”时, Synplify把额外属性写入 EDIF之中,要观察的内容包括该模块最近被综合时的时间戳。如果从上一次运行开始模块一直没有发生变化,旧的时间戳被存入EDIF之中。每个标有“locked, physical”的编辑点将含有这样一个时间戳。赛灵思ISE 9.1i 拾取该时间戳,与以前的布局和布线时间戳进行比较,并且只在发生改变的模块上进行增量布局和布线。

总结和优点

一般说来,保存一项设计要比重新实现一项设计更快。因此,如果大部分设计能通过采用Partitions或SmartGuide进行保存,实现这项设计所需的时间将会更少。在用于测试这些技术的广泛的工具套件中平均运行时间的改善,比最初的实现要快 2.5倍。例如,如果一项设计要花3个小时实现,那么,利用设计保存的实现所需时间就要少1个小时。在一些最佳的情形下,运行时间比最初实现要快到6倍之多。

设计保存的另一个优点是减少了验证。如果一个设计模块被严格地保存,那么,那部分设计在设计修改后就不需要再重新验证。因为已保存的实现与前一次的实现是完全相同的,布局、布线和时序是相同的,这样重新验证就没有必要了。

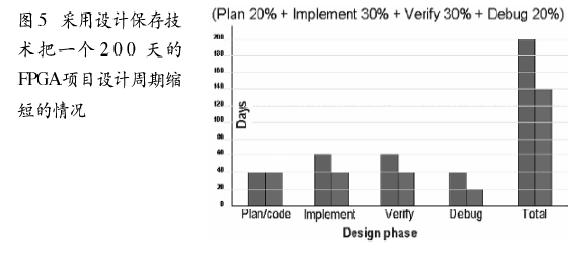

要花大约200天来实现的FPGA设计通常涉及设计定义、实现、验证和调试。分配到每个阶段的预计时间如图5所示。采用设计保存技术,就有可能使解决问题所花费的时间减少几个月。这是基于这样的假定:FPGA 的实现时间是几个小时,因此,运行时间可能被减少。它还假定该设计采用基于模块的验证测试基准,因此,在该设计内已保存的模块不需要被重新验证。如果一项设计采用了这种技术,采用SmartCompile技术获得解决方案所花费的时间就被大幅缩短。

赛灵思 SmartCompile 相关文章:

- 迅猛发展的模拟混合信号技术(02-15)

- 选择合适的转换器:JESD204B与LVDS对比(12-15)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)