利用SmartCompile和赛灵思的设计工具进行设计保存

在FPGA环境下,设计保存实施比较复杂,需要保存的事项包括:一项设计的HDL描述、一个模块的综合网表、约束文件内的布局信息,以及在局部比特文件中的配置数据。赛灵思集成软件环境ISE 9.1i 软件以新的SmartCompile 技术为特色,其中包含两种新的方法:SmartGuide和Partitions,这两种方法可以保存像布局或布线这样的设计执行数据,并且可以减少解决问题所花费的时间。

SmartGuide采用命名和拓朴匹配技术来识别一个FPGA设计中相对于以前的实现还没有发生改变的各个部分。在新的和已修改过的设计被重新实现时,设计中匹配元器件得到了保存。

Partitions 采用的技术中,FPGA 设计的模块实例被自动分析,接着,与以前的模块实现比较,确定该模块实例是最新的还是过时的。如果Partition 是过时的,它也完全可以重新实现且不发生保存。如果Partition是最新的,它可从以前的实现中被严格地复制且(从综合网表通过布线)完整地保存布局和布线运行时间。

SmartGuide如何运作?

SmartGuide工作在像查找表(LUT)和触发器这样的FPGA中最低级的物理单元上。这些单元及其连通性被依次匹配和保存。

要成功引导的第一步是对已经作出较小变更的设计综合一个一致的网表。例如,减法器等式regAB=(A"B),可以被综合成Msub_sub0001的逻辑名称。下一个减数就称为Msub_sub0002,并且依此类推。在引入新减数的设计中的任何变更都可能造成设计中所有减数的重新命名。为了解决这个问题,像Synplicity 公司的Synplify和Synplify Pro以及赛灵思公司的XST这样的综合工具,已经改变了逻辑命名的惯例。利用这些工具,无论用户有没有对RTL进行变更或进行了小的变更,逻辑命名从一个综合运行到下一个综合都变得更加可以预测。按照以上的实例, 减法逻辑就被命名为Msub_regAB_sub0001。通过采用在逻辑中的寄存器名,就能防止改变到其它的减数。

综合命名惯例的另一项增强措施是以本地而不是全局上下文为基础。在RTL出现小的变化以及设计沿着非关键路径重新综合时,这可能有所帮助。在综合之后,与非关键时序路径相关的逻辑被修改,而机器给未改变逻辑产生的实例名称保持不变。综合网表变化被本地化到网表内的已修改的或新的逻辑。最优化一向是可复制的,这是因为它们以本地逻辑为基础。例如,作为最优化过程的一个部分,Synplicity的 Synplify/Pro目前创建路径组(path groups),它是被分别最优化的各个逻辑组。当逻辑在非关键时序路径上优化时,只有受影响的路径组被改变,以最小化对综合网表的影响。

在生成综合网表后,ISE 9.1i中的实现工具会处理网表,并把它转换成针对特定FPGA 架构的经布局和布线的设计。在匹配过程中会发生引导,所有的元器件以匹配元器件名称为基础被引导。如果一个元器件在目前的实现和引导设计中都有相同的名称,那么,该元器件就能被成功地引导。该元器件可能有不同的LUT方程式或引在生成综合网表后,ISE 9.1i中的实现工具会处理网表,并把它转换成针对特定FPGA 架构的经布局和布线的设计。在匹配过程中会发生引导,所有的元器件以匹配元器件名称为基础被引导。如果一个元器件在目前的实现和引导设计中都有相同的名称,那么,该元器件就能被成功地引导。该元器件可能有不同的LUT方程式或引脚,并仍可以成功地被引导。

如果在当前实现和引导设计中的源和负载引脚是相同的,就能对网络进行引导。这消除了对两次实现之间的网络名称要保持一致的依赖。它也极大地增加了成功引导网络的机率。

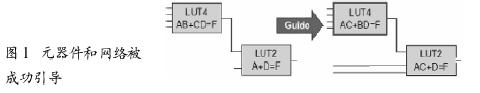

如图1所示,例如,LUT4的逻辑等式已经被修改。LUT4将被引导,因为即使它的逻辑等式是不同的,它的相关名称也没有被改变。LUT4和LUT2 之间的布线将被引导,这是因为LUT4 和 LUT2之间的连通性没有被修改。

在元器件和网络被引导之后,新的和经修改的元器件及网络被增加到设计中。网表中没有变更的那部分在某些情况下必须被重新布局和布线,但是,这只在设计变化引起电路中另一个部分出现一个重大路径时序冲突的情况下。正是因为该原因,这是一个清除阶段。如果存在关键路径的时序冲突,就会有一些引导逻辑的移动以确定时序。在来自新的和已修改逻辑的关键路径上的清除阶段可能迫使引导逻辑的移动。这个清除阶段极大地增加成功实现一项设计的机率,该设计以稍微降低一些逻辑的保存为代价,以满足时序约束的要求。

Partition如何运作?

为了做到准确无误的保存,设计工程师必须对模块实例设置一个被称为Partition的属性。这将把Partition与该设计的其它部分相隔离。通过隔离模块实例,其接口

赛灵思 SmartCompile 相关文章:

- 迅猛发展的模拟混合信号技术(02-15)

- 选择合适的转换器:JESD204B与LVDS对比(12-15)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)