将ADC介接到高效能运算放大器

前言:一般而言,用来驱动现今高分辨率类比/数码转换器的电源都是拥有数百欧姆或以上的AC或DC负载。因此,一个具备有高输入阻抗(数百万欧姆)和低输出阻抗的运算放大器便成为ADC驱动器输入的最佳选择。ADC驱动器可作为缓冲器和低通滤波器之应用,以减低系统的整体杂讯。

随着讯号在电路板的布线和冗长电缆上传送,系统杂讯会积聚在讯号里,而一个差动ADC会拒绝任何看来像共模电压的讯号杂讯。相比起单端的讯号,采用差动讯号有好几个优点。首先,差动讯号可将ADC的动态范围增大一倍。其次,它可提供更佳的谐波失真效能。现今有几个方法可从一个双重运算放大器配置产生出差动讯号。其中一种方法是采用单端/差动转换技术,而另一种则需动用差动输入源。为了利用完全的ADC的动态范围,ADC的输入必须被驱动至满刻度的输入电压。

本文将会讨论三种不同的ADC驱动器架构:单到单、单端到差动和差动到差动。主要目的是希望能扼要地提供一切用ADC介接高效能运算放大器的资料。

讯号路径的必要组件

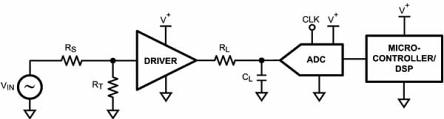

以下会把讯号路径中的类比前端设计之几个组成部份一起讨论。典型讯号路径的类比前端包括有一个用来驱动ADC的运算放大器、一个RC滤波器、ADC和微控制器或数码讯号处理器(DSP)。

图1:典型讯号路径的类比前端方块图

现实世界中的输入源会带有不理想的阻抗,因此需依赖一个很低输出阻抗的缓冲放大器来驱动ADC的输入。然而,外置的RL-CL滤波器会作用为一个抗叠频滤波器,以帮助减低ADC驱动器的杂讯频宽,以及缓冲由ADC取样和保持电路所引致的充电瞬时。为了尽量减低输入电压的跌降,外置的并列电容(CL)必须比ADC的内置输入电容大10倍,而同时外置的串行电容(RL)亦必须够大以固定发生在运算放大器输出的相位延迟,从而维持电路的稳定性。对于大部份的应用而言,在运算放大器输出和ADC输入之间用一个串行隔离电阻来连接,都可以带来益处,因为这个串行电阻可有助限制运算放大器的输出电流,而为这个串行电阻选定数值是一项非常重要的工作。

一个比较高的电阻值将会增加运算放大器的负载阻抗,从而改善运算放大器的整体谐波失真(THD)效能。可是,ADC通常都较喜欢以一个低阻抗的源来驱动。因此,必须为这个串行电阻找出最佳的数值,才能一同为运算放大器和ADC带来最佳的THD、SNR和SFDR效能。当把ADC连接到一个运算放大器时,最重要是了解将会影响到效能的规格。现今的ADC规格,例如是THD、SNR、设置时间和SFDR等,它们均对滤波、测量、视频和重现应用很关键。高效能运算放大器的设置时间、THD和杂讯效能必须比被驱动的ADC的效能更好,以确保系统的精确度以及将错误减至最低或甚至消除。

在本文中, LMH6611或LMH6618单一运算放大器会被用来驱动单通道的ADC121S101 类比/数码转换器,而另一方面,LMH6612或LMH6619双重运算放大器会被用来驱动差动输入的ADC121S625或ADC121S705类比/数码转换器。这些放大器的应用范围相当广泛,特别适用于要求高速、低供电电流、低杂讯,以及需要驱动复杂ADC和视频负载的应用。

运算放大器和ADC的重要规格

在现实中,有些系统应用会要求低THD、低SFDR和宽阔动态范围(SNR),而另一些则可能要求高SNR,并且可能会牺牲THD和SFDR的效能来换取更佳的杂讯效能。

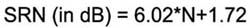

对于运算放大器和ADC而言,杂讯都是一项很重要的规格。这里有三个主要影响ADC整体效能的杂讯来源:量化杂讯--是由ADC本身所产生的杂讯(尤其在较高的频率下),以及由应用电路所产生的杂讯。输入源的阻抗可影响运算放大器的杂讯效能。理论上,ADC的讯号与杂讯的比例(SNR)可用下列算式计算出来:

算式中的N是ADC的分辨率。例如根据这条算式,一个12位的ADC便拥有74dB的SNR。可是,实际的SNR数值会大约是72dB。为获得更佳的SNR,ADC驱动器杂讯应该愈小愈好。LMH6611/LMH6612/LMH6618/LMH6619的低电压杂讯仅为10 nV/ 。

运算放大器和ADC的整体设置时间必须在1 LSB之内,而LMH6618/LMH6619和LMH6611/LMH6612的0.01%设置时间分别为120ns和100ns。

此外,ADC驱动器的THD必须低于ADC。LMH6618/LMH6619在2VPP输出和100 KHz输入频率时的SFDR为100dBc,而LMH6611/LMH6612在2VPP输出和1 MHz 输入频率时的SFDR则为90dBc。

讯号/杂讯比和失真(SINAD)是一个参数,它结合了SNR和THD这两个规格。SINAD是指输出讯号的RMS值与所有其它低于时钟频率一半的光谱成份之RMS值之比例,这包括谐波但不包括DC,以及可凭下列算式从SNR和THR中计算出来:

由于SINAD是将输入频率与所有不良频率成份作比较,所以它其实是ADC动态效

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)