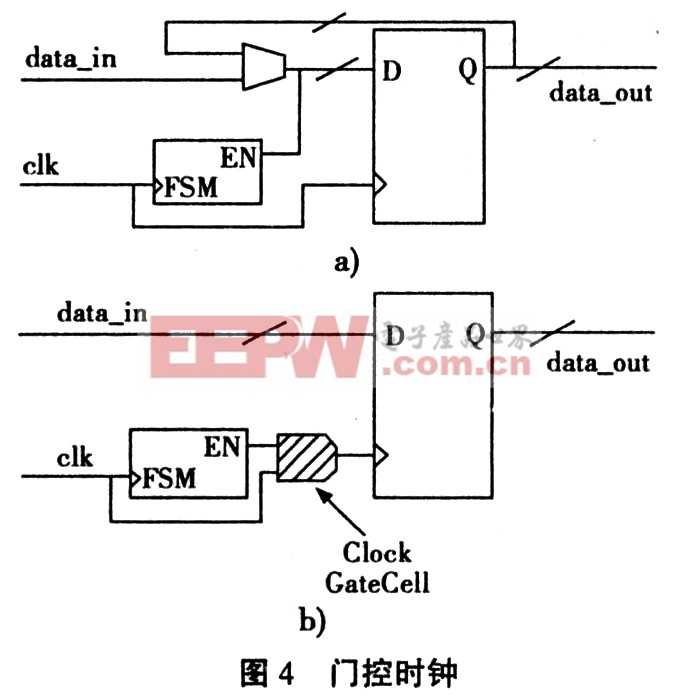

门控时钟是通过一个控制信号来使能寄存器的时钟端,当使能信号有效时时钟翻转,否则时钟保持稳定,让部分电路处于空闲状态,达到节省功耗的目的。图4给出了门控时钟的示意图,图(a)是传统的寄存器设计,无论数据端输入数据更新与否,寄存器的时钟端始终处于翻转状态,如果寄存器需要保持原来的状态,还需要将寄存器的输出数据反馈回输入端与输入信号进行选操作,由控制逻辑产生的选择信号En决定寄存器输出数据。图(b)是采用门控时钟后的电路,En作为使能信号,只有当它有效时,寄存器实际的时钟输入端才会产生脉冲,将输入的数据更新到寄存器。门控时钟可以切断空闲时钟,减小时钟线的负载电容,降低动态功耗。同时在控制电路的设计中,可以采用门控时钟对分块的存储阵列进行控制。通过门控时钟控制信号使能,某一时刻仅有要使用的块被选中激活,其他块处于待命状态,这样就大大降低了整个寄存器堆的功耗了。

2.4 灵敏放大器

寄存器堆中的灵敏放大器是存储单元读操作中的关键部分,高速的灵敏放大电路可以降低位线上的电压摆幅,减小敏感放大器功耗,降低读操作的时间。

读操作位线功耗可由下式估算:

其中,Lcell是存储单元的电流,Tw1是字线上脉冲的宽度。

要降低读操作的功耗,由上式可知,只要降低Lcell和Tw1即可。而Icell必须要大于灵敏放大器工作的输入电流。因此,尽量采用低工作电流的灵敏放大器成为减小读操作位线功耗的重要途径。

通常的电压型灵敏运放为了避免电压的小幅摆动,往往采用层次结构,但这样带来的不利是延时和功耗的增加,电路变得复杂。电流型的灵敏运放电路能够快速检测到位线上电流的小幅摆动,而且可以降低读操作的功耗,成为高速SRAM设计的首选。当它工作时,位线电平几乎保持不变,因而基本上消除了位线电容充放电引起的功耗,但是代之以短路电流功耗,如果不对接地电流进行限制,就会大大抵消抑制位线电容充放电带来的功耗节省,甚至可能增加功耗。差分电流型的灵敏运放电路能提高寄存器堆的读取速度,并且有效地降低灵敏放大器功耗。因此,针对不同规模的寄存器堆,要选择合适类型的灵敏放大器,才能达到高速低功耗的要求。

3 总结

多端口寄存器堆的低功耗不能仅仅针对某个单元或某个部分进行,而应该结合它的基本组成单元和它的电路结构,分析其功耗组成,从中找到节约功耗的有效方法。本文总结了几种降低多端口寄存器堆功耗的方案,对各个组成电路结构,有针对性地进行功耗优化,包括降低字位线电压摆幅,减小负载电容,采用门控时钟,以及选用合适的灵敏放大器等方法,从而达到降低寄存器堆总功耗的目的。