用于高速ADC的低抖动时钟稳定电路的设计

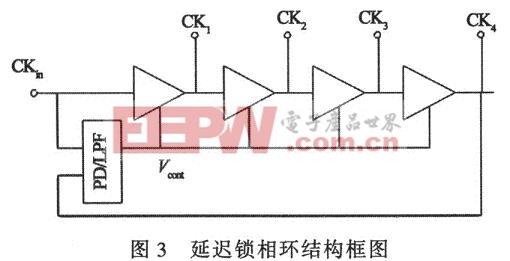

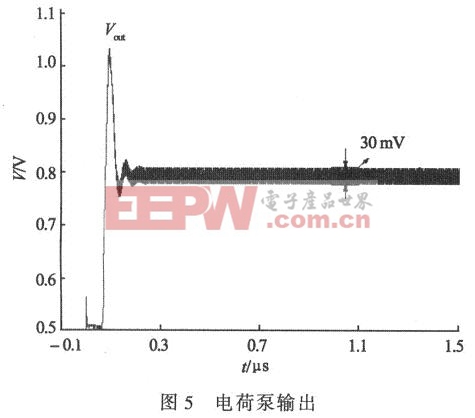

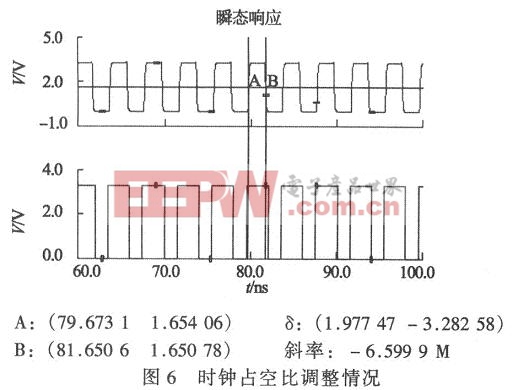

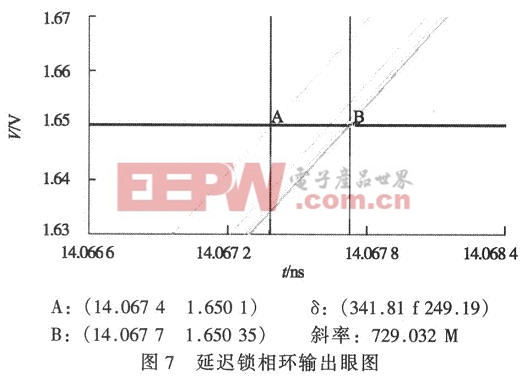

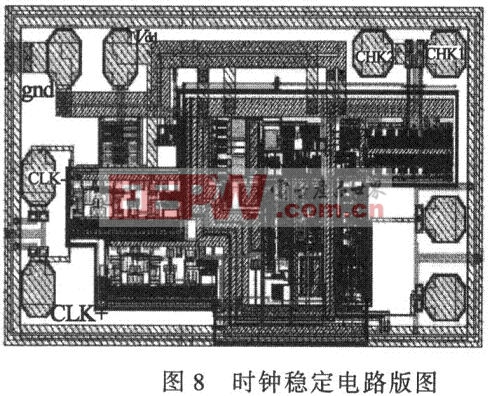

框图如图3所示。其中CKin和CK4之间的相位差用一个鉴相器来检测,产生成比例的平均电压Vcont,通过这个电压的负反馈来调节每一级的延时。对于大的环路增益,CKin和CK4之间的相位差很小,即这四级电路将时钟几乎准确地延时了一个周期,从而建立了准确的时钟沿间隔。这种电路结构被称为延迟锁相环,是为了强调它采用了一个电压控制延迟线电路而不是VCO。实际上,为获得无穷大的环路增益,需要在PD和LPF之间插入电荷泵。 延迟线与振荡器相比受噪声较小,这是因为波形中被损坏的过零点在延迟线的末端就消失了,而在振荡器电路中又会再循环,因而产生更多的损坏;其次,DLL中控制电压的变化能迅速改变延迟时间。总之,PLL中用到的振荡器存在不稳定性和相位偏移的积累,因而在补偿时钟分别造成的时间延迟时,会降低PLL的性能。因此DLL的稳定性和稳定速度等问题比PLL要好。 2 电路设计 2.1 电路原理图 图4中,虚框a中的电路为鉴相器(PD),S为鉴相器的控制端,只有为低电平时,鉴相器才起作用。压控延迟线的输出端VCDLout为鉴相器的输入端,这个信号与时钟信号CLK进行比较,得出输出信号A。由于S端低电平有效,CLK信号就是与它的反相延迟信号与非进入后面的锁存结构。其实就是检测下沿与另一个下沿组成一个占空比接近50%的时钟信号。A信号经过一个电阻R传入电荷泵中(其实在鉴相器的输出端可以加一个反相器再加一个电容滤波)。虚框b为电荷泵,由一个运算放大器组成。其中F端接一个电压值为基准的一半的电压,即为1.65 V。 由m0、ml、m2、m3组成的镜像是运算放大器的启动电路,在运算放大器不工作时对电容C1充电。电阻R1和电容C1构成一个RC滤波器,对信号起到滤波的作用。m4、m5、m6三个晶体管构成DLL的延迟线(VCDL)。在这个电路中只需要一级延迟就足够了。在这个延迟线旁边的电容C2的值越大,则延迟越多。C2旁边三个反相器构成一个锁存结构,它的主要作用就是输出一个比较理想的方波。 2. 2电路仿真与分析 对图4的电路,在Cadence spectre环境下进行了仿真。输入电平的周期为4 ns,时钟占空比为45%,基准电压为3.3 V。运算放大器与电容c.组成电荷泵。电荷泵的输出见图5。时钟稳定电路稳定工作,Vout有30 mV的波动,Vout波动越小表示压控延迟线时钟输出的抖动越小。 此外,还可以得到,运算放大器的闭环增益为75.074 9 dB。0 dB对应的相位为一109.818°,所以它的相位裕度为70.182°。显然,该运算放大器的参数是比较好的。 图6为时钟占空比调整情况。从图中可以看出该DLL能调整占空比到49.4%(1.977 4/4≈49.5%)。实际上该时钟稳定电路在时钟周期4 ns时,能调节25%~75%的占空比接近于50%左右;而在时钟周期10 ns时,可调节的范围达到10%~90%。 图7为延迟锁相环的输出眼图。其实在A、B之间有几百条上升沿。从图中可以看出,峰.峰值抖动为341.8l fs。对于250 M这个抖动值已经相当小了。 3 版图设计 利用JAZZ提供的PDK进行工艺接口,版图设计由该公司提供相应规则,具体针对线宽、接触孔、通孔、线距等作了相关规定,并且设计过程中充分利用该公司提供的Pcell作相应的版图设计,这样相应工作得到了很多的简化。具体的设计规则涉及IP问题,故略去。本文给出时钟稳定电路的整个版图,如图8所示。 该芯片总面积为0.74 mm×1.44 mm。其中,最左边的CLK一,CLK+为输入端,本文只用到CLK一一端作为输入端就足够了;右上角的CHKl、CHK2为输出的大管子;最中间为运算放大器。 4 结语 本文介绍了用一个简单的延迟锁相环来实现高速A/D转换器中的时钟稳定电路。该延迟锁相环具有两个作用:(1)调节采样时钟占空比;(2)控制采样时钟的抖动。本文以一些典型的基奉模拟IC为设计基础,着重对延迟锁相环电路的各个单元电路设计逐一进行了分析和研究,并对总体电路进行了功能和参数的模拟分析,其结果较为满意。在此基础上进行了工艺及版图设计和分析,在完成工艺版图设计后,采用DRC、ERC、Calibre、Extract和LVS等CAD工具对版图进行了参数提取及验证工作,保证了电路和版图的一致性。

高速A D转换器 延迟锁相环 占空比稳定 时钟抖动 相关文章:

- 8位高速A/D转换器TLC5510的应用(02-16)

- 用差分放大器来驱动高速ADC(03-28)

- 一种用于高速ADC的采样保持电源电路的设计(10-21)

- 高速ADC的性能测试(08-26)

- 高速ADC电源设计方案(08-28)

- 基于高速ADC的脉冲测量(12-08)