基于FPGA的航空总线协议接口设计

数据总线是飞机航电系统中首先运用的数字电子设备之一,其典型代表是飞机内部时分制指令/响应式多路传输数据总线MIL-STD-1553B(简称1553B)。它利用一条屏蔽的双绞线进行带有时钟信息的数据传输。高可靠性1553B已成为我国航空航天领域广泛采用的军用总线标准。由于1553B总线协议控制器基本依赖于进口的专用器件,价格昂贵,还受到限制,并且这些器件需要外围的硬件电路配合工作,如果完成整个总线接口板的设计,还需要单独的MCU,集成度不高,这样就在某种程度上限制了设计能力。随着嵌入式技术的发展,可编程片上系统设计SoPC技术已广泛应用于诸多领域。这里采用SoPC技术,以Virtex-II Pro FPGA为核心,实现1553B航空总线传输协议的接口逻辑设计。

2 1553B航空总线传输协议标准

目前广泛采用的1553B标准是根据1973年军标1553原版基础上发展。1553B是一种集中控制式、飞机内部时分指令/响应型多路串行数据总线标准。具有高可靠性和灵活性。已经成为现代航空机载系统设备互联的关键技术。广泛应用于飞机、舰船等武器平台。1553B数据总线的传输速率为1Mb/s,协议规定3种字:命令字、数据字和状态字。字的长度为20 bit,且由同步头(3 bit)消息块(16 bit)和奇偶位(1 bit)3部分组成。信息量最大长度为32。总线系统由一个总线控制器(BC)与不多于31个的远程终端(RT)组成,有时系统中还可加入总线监控器(MT)。总线上传输的信息格式主要有BC到RT,RT到BC,RT到RT,以及广播方式和系统控制方式。

3 系统设计

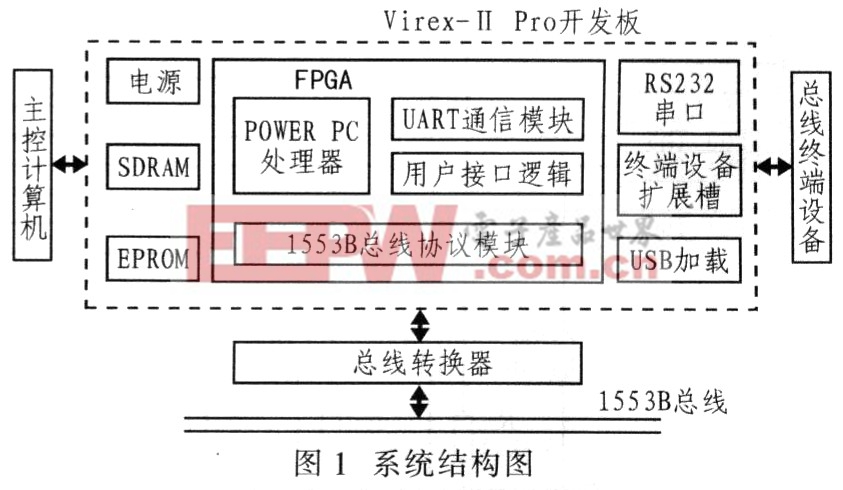

该系统采用Xilinx公司的Virtex-II Pm XC2VP30 FPGA为核心,该器件内部带有2个PowerPC 405处理器核。总线接口协议实现是基于Xilinx Virtex-II Pro开发系统平台,Virtex-II Pro开发平台是整个系统的核心。这样可以快速搭建1553B总线实现平台。系统的硬件平台主要由Vinex-II Pro开发板、总线转换器、总线终端设备和主控计算机构成,系统结构如图1所示。

在系统开发中,为了提高开发效率,同时系统主要验证的就是1553B总线协议模块,因此可充分利用Xilinx公司的Virtex-II Pro开发板。开发板上具有丰富的资源,主要包括:XC2VP30器件、SDRAM (可扩展到2 GB)、高速SelectMAPFPGA配置PROM、RS232串口、嵌入平台的USB配置端口、高速系统扩展接口(与FPGA的I/O引脚相连)并可选择差分或单端模式、PS2接口、AC97音频接口、板上10/100 M以太网设备等等。这些丰富的板上资源为1553B总线协议逻辑的开发提供支持。

1553B总线协议开发主要在FPGA器件中开发,因此FPGA本身性能的好坏将影响系统的开发。XC2VP30内部具有2个PowerPC 405处理器核、13 969个Slices、分布式RAM为428 KB、136个乘法器单元、块RAM为2 448 KB、8个DCM、8个多吉比特收发器。因此,选用XC2VP30FPGA完全满足1553B总线逻辑开发需求。

该系统设计采用Virtex-II Pro系列XC12VP30型FPGA,而FPGA的配置则是硬件设计中很关键的问题。FPGA配置是对其内容进行编程。采用SRAM工艺的FPGA,每次上电后都需重新配置。XC2VP30通过模式引脚选择配置模式,其中M2、M1和M0是专用引脚,HSWAP_EN和配置模式引脚相组合,决定I/O引脚在配置过程中是否具有上拉功能。默认情况下,HSWAP_EN置为高电平,此时在配置过程中关闭I/O引脚的上拉功能;当其置为低电平时,I/O引脚具有上拉功能。当选择某些配置模式时,CCLK可作为FPGA的信号输出引脚,也可作为外部时钟的输入信号,这些引脚不受VCCO的影响,而是采用2.5 V的辅助电源(VCCAUX)。

图2给出的是FPGA配置引脚连接电路图。XC2VP30支持5种配置模式,分别是Slave-serial模式、Master-serial模式、Slave SelectMAP模式、MasterSelectMAP模式和Boundary-Scan (IEEE 1532/IEEE 1149)模式。通过调整配置引脚MO、M1、M2调整配置模式。该系统设计只提供两种配置模式,在XC2VP30的配置电路中将M0引脚拉为高电平,这样只能选择MasterSelectMAP模式和Boundary-Scan模式(即边界扫描模式)。Master SelectMAP模式是SelectMAP模式的主版本模式,在由XC2VP30所提供的CCLK信号的作用下,器件通过字节宽度数据总线即配置器件XCF32P的[D7:D0],除了CCLK是由FPGA提供之外,配置时序与Slave SelectMAP模式相似。在边界扫描模式下,XC2VP30通过专用配置引脚CCLK,DONE,PROG_B,TDI,TDO,MS,TCK按照IEEE 1149.1标准进行配置。

4 1553B航空总线协议接口的SoPC设计

SoPC的开发设计与传统嵌入式系统设计不同,分为硬件开发和软件开发。系统设计思想是充分利用FPGA片上资源,以PPC405处理器硬核为核心,1553B接口逻辑为主要设计内容的SoPC系统,在FPGA内部实现系统的总线架构、外设接口、编码/解码、消息处理模块等系统部件和功能,各功能部件在FPGA的内部都是通过IP核的形式连接在一起的。Xilinx为了用户能够将自行编写的逻辑方便连接到OPB总线上,提供总线与用户逻辑之间的接口,即IPIF(IP Interface,IP接口),利用IPIF便可解决总线接口信号,总线协议以及其他接口问题。

4.1 曼彻斯特编码,解码模块

曼彻斯特码编码/解码是1553B总线接口重要组成部分,曼彻斯特码编解码模块设计将直接影响总线接口的性能。系统编码模块完成曼彻斯特码的编解码,并检测错误。它能够接收具有有效同步字头的曼彻斯特码,并对其译码,识别类型和串并转换、奇偶校验等;编码模块能将处理器输出的并行二进制数据进行曼彻斯特码编码,再加上同步字头及奇偶位,从而输出满足符合1553B标准的字。

曼彻斯特码是一种广泛应用于航空电子综合系统中的总线数据传输的双极性码。它在每个码位中点存在一个跳变,1信号是一个由1到0的负跳沿,而0信号是由0到1的正跳沿。在MIL-STD-1553B协议中其数据格式如图3所示。

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)