一种低电压低温漂的基准电流源

0 引 言

基准电流源在模拟和混合信号系统中占有非常重要的地位,在A/D转换器,D/A转换器以及很多模拟电路如运算放大器、滤波器等电路中起着至关重要的作用。目前出现了几种基准电流的设计方式。文献[1]提出的电路测试的温度系数为50 ppm/℃。文献[2]是一种非带隙电路通过二阶温度补偿产生基准电流,温度系数为28 ppm/℃。文献[3]提出一种低温漂低电源电压调整率CMOS基准电流源,其温度系数为6.9 ppm/℃,但温度范围为-40~85℃,相对变化范围较小。文献[4]利用带隙基准电路产生正温系数基准电压和迁移率的负温效应相互抵消,产生基准电流。但温度系数仍大于15 ppm/℃。在此设计一种CMOS基准电流源,首先通过二阶补偿的低压带隙基准电路得到基准电压,然后由这个基准电压偏置NMOS的输出管得到基准电流。这个输出管将被设计工作在零温漂点附近,在零温漂点上,通过输出管的阈值电压和迁移率随温度的变化率相互补偿,从而减小了温度对偏置电流的影响。

1 零温漂偏置点设计

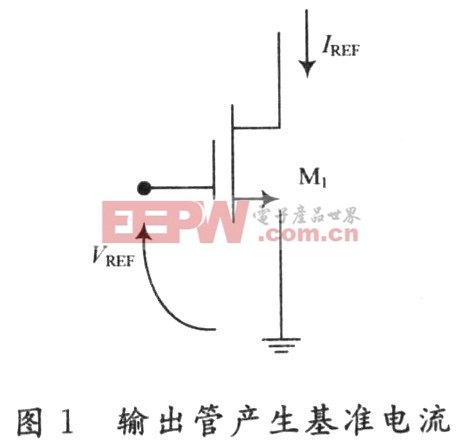

作为一个电流源应有非常高的输出电阻,所以将电流源设置在输出管的漏端。如图1所示,基准电流的稳定性主要取决于偏置电压VREF,M1的阈值电压VTH1以及迁移率μn。当输出管M1工作在饱和区时,基准电流可表示为:

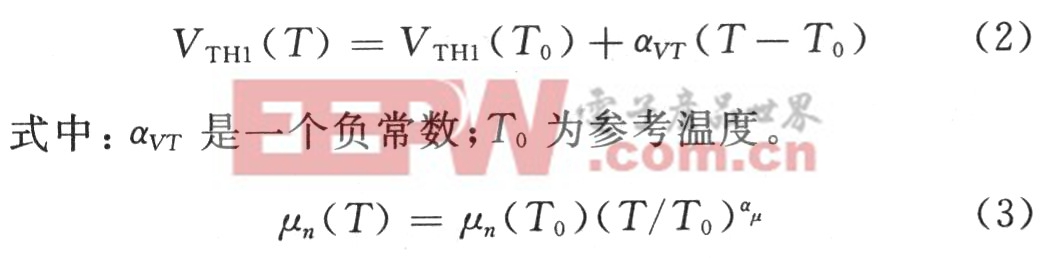

式中:Cox为单位面积的栅氧化层电容;W1和L1分别为沟道的有效宽度和长度;文中的VREF是由一个与温度基本无关的二阶补偿的低压带隙基准电路得到的。但阈值电压VTH1以及迁移率μn都和温度有关,当温度在0~100℃时,VTH1随温度的最大变化值有150 mV左右。从式(1)可以看出,IREF会随温度有较大的变化。但当输出管工作在零温漂的偏置点上时,就可以得到一个与温度基本无关的基准电流源,式(2)和式(3)分别给出阈值电压VTH1以及迁移率μn与温度的关系:

式中:αμ也是一个负常数。

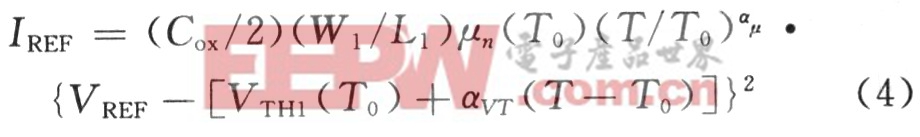

将式(2)和式(3)代入式(1)得:

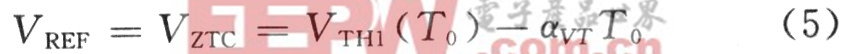

由于NMOS的沟道掺杂浓度在1015~1016cm-3左右,这时的负常数αμ将十分接近-2。在这种情况下,如果:

式中:VZTC是当输出管工作在零温漂点的偏置电压。将式(5)代入式(4)就可以得到一个基本与温度无关的基准电流源。

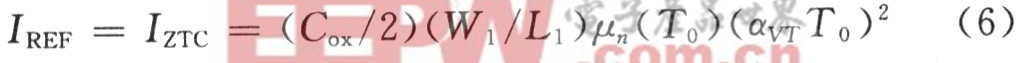

式中:IZTC是当输出管工作在零温漂点的基准电流。

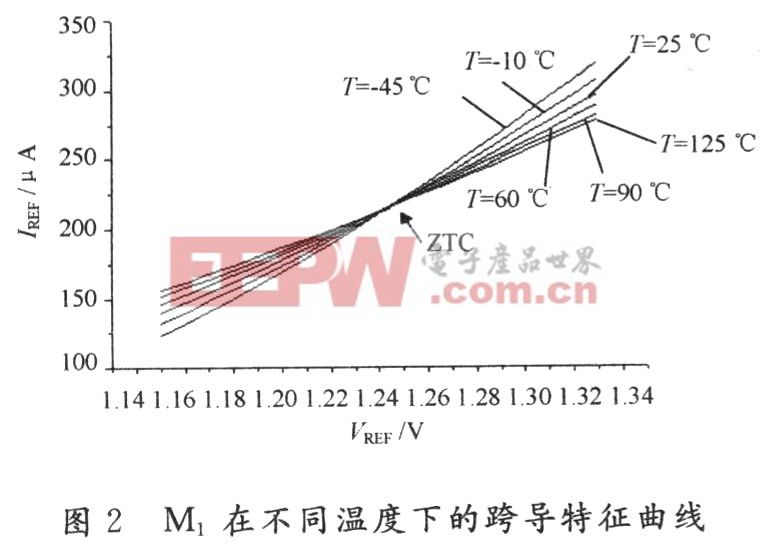

图2给出在不同的温度下,输出管M1的漏电流随栅电压变化的特征曲线,结果表明在CSMC 0.5/μmCMOS工艺中,输出管M1的零温漂点为(IZTC=215.4μA,VZTC=1.244 4 V)。

现在需要得到一个偏置电压VREF。VREF不但要与温度无关,而且必须等于VZTC,使得输出管M1工作在零温漂点(ZTC),产生一个与温度无关的基准电流IREF。这个偏置电压可以通过下述的二阶补偿的低压带隙基准电路得到。

2 二阶补偿的低压带隙基准电路

2.1 低压带隙基准电路

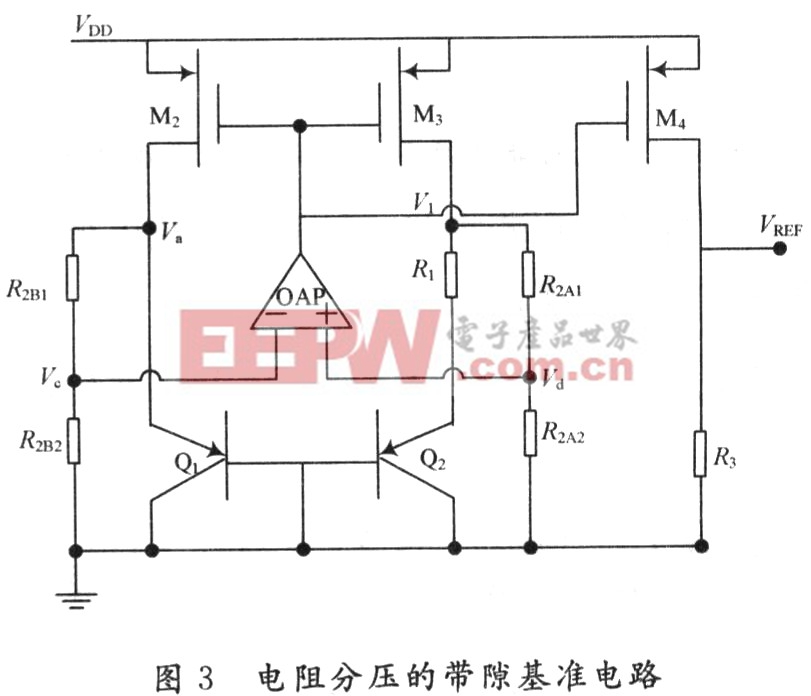

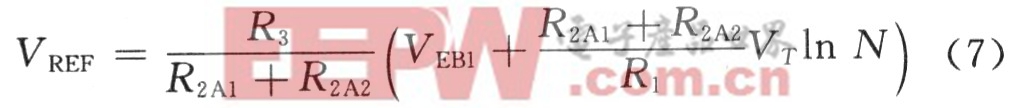

传统带隙基准源设计的基本思想是选择适当的系数,将具有正温度特性的热电压VT与具有负温度特性的双极型晶体管的VBE相加,从而得到一个与温度无关的近似输出,但在低压情况下,这种模式的带隙基准电路将受到限制。文献[7]给出一种电流模式,采用电阻分压得到的一个低压的带隙基准电路。如图3所示,该电路将正温度系数和负温度系数两电流之和通过电流镜镜像到输出端,得到基本与温度无关的基准电压。

调整R1的阻值使Va和Vb分别大于0.6 V,晶体管工作在指数区,同时利用R2B1,R2B2及R2A1,R2A2,进行分压,得到较小电压的Vc和Vd作为运放的输入电平。其中R2B1=R2A1,R2B2=R2A2,所以Va=Vb,Vc=Vd。可以推导出图3中带隙基准输出电压VREF:

2.2 二阶温度补偿

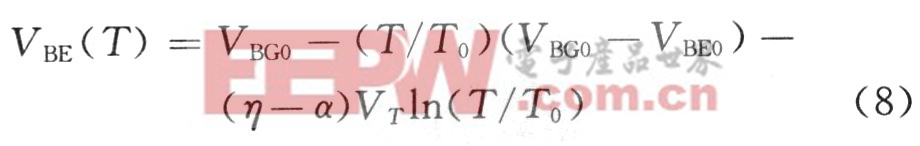

由文献[8]可知,双极型晶体管的VBE并不是随着温度线性变化的,其温度特性可表示为:

式中:VBG0是在温度为0 K时外推而得到的PN结二极管电压;T是绝对温度;T0是参考温度;VBE0是在温度为T0时的发射结电压;η是与工艺有关且与温度无关的常数;α的值与集电极电流Ic的温度特性有关(当Ic与温度成正比,即PTAT电流时,α=1;当Ic是与温度无关的电流时,α=0)。

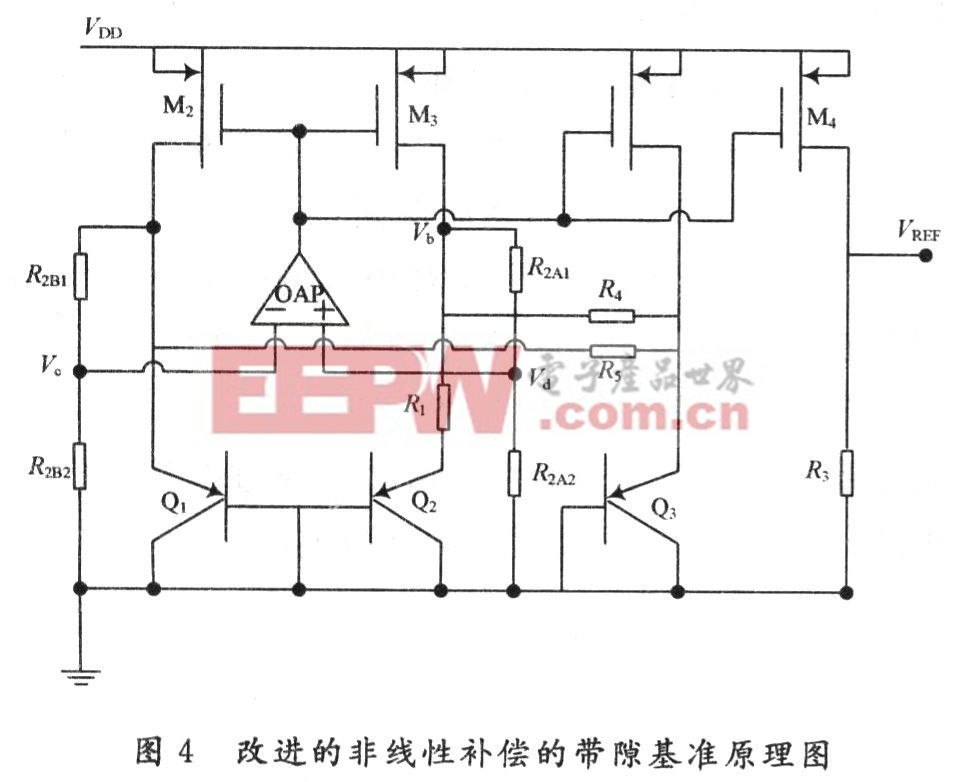

文献[9]运用这个原理对电路进行了二阶温度补偿,但在低电源电压的情况下,文献[8]中的电路将受到限制。在此将这种二阶温度补偿的方法运用到图3的带隙基准电路中,改进后的电路图如图4所示。

从图4可以发现若将Vbe3与Vbe1相减可得到随温度非线性变化的电压项:

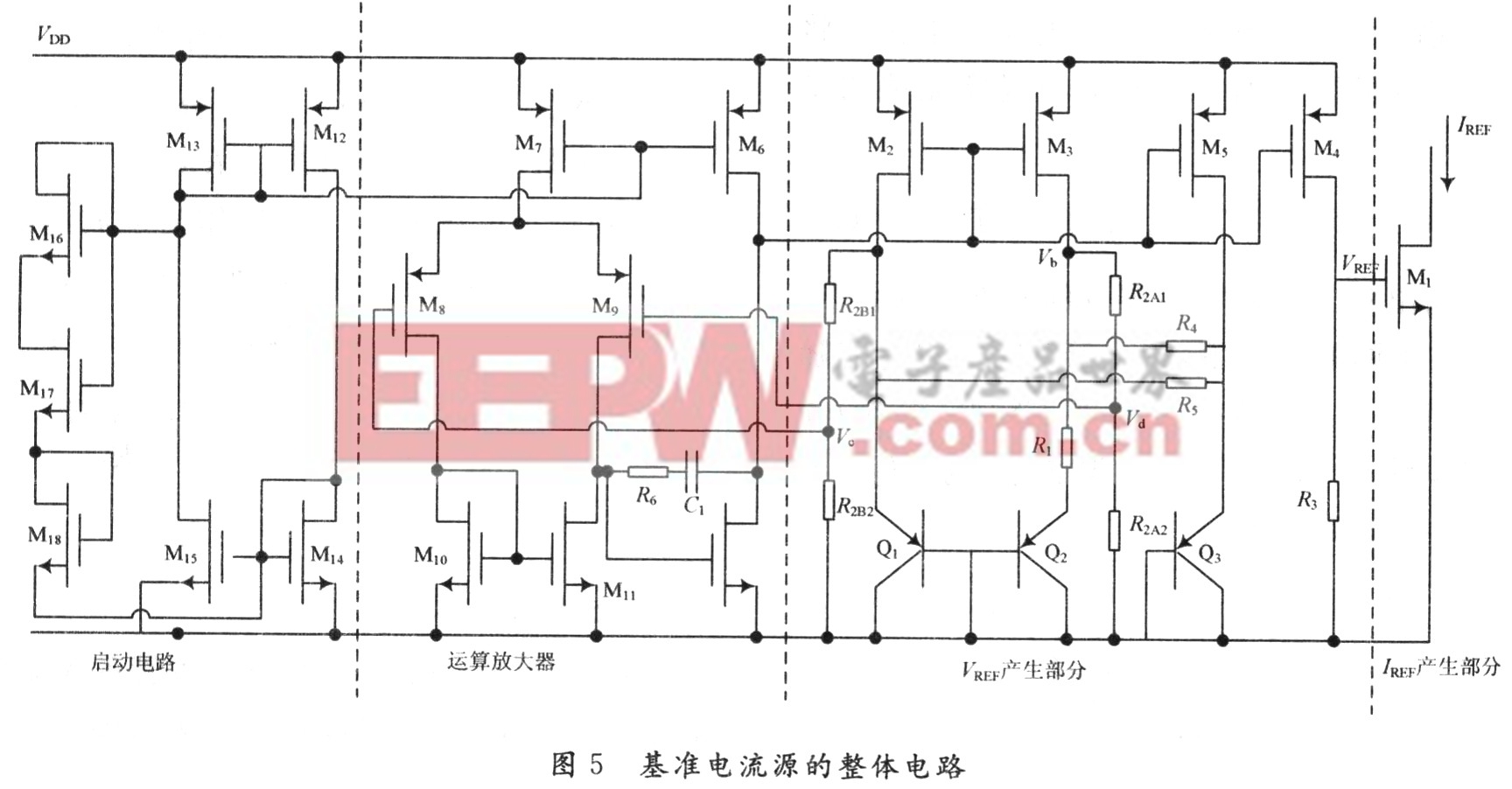

3 基准电流源的整体电路

图5为基准电流源的整体电路,由二阶补偿的低压带隙基准电路得到VREF接到输出管M1的栅端,从而产生一个零温漂的基准电流源。为了提高对电源噪声的抑制能力,带隙基准电路中运算放大器的输入管使用PMOS的差动对,由于是两级的运放,所以有必要加一个电容进行补偿。

4 测试结果及分析

基于CSMC 0.5μm CMOS工艺,对上述电路进行流片,电路的显微照片如图6所示。

- 便携式电源产品中的电池充电器发展趋势(07-07)

- 低电压差分信号(LVDS)原理和设计(01-10)

- LVDS信号原理和设计(03-22)

- 低电压大电流的线性解决方案分析(04-22)

- 几种实用的低电压冗余电源方案的设计(08-10)

- 双低电压理想二极管控制器(10-16)