一种通用中频数字化接收机的实现

摘要:为满足雷达中频数字化接收机通用性设计要求,给出基于可编程的四通道数字下变频器ISL5416结合高速A/D器件AD6645实现通用中频数字接收机的设计方案。利用AD6645实现直接中频采样,在ISL5416中完成频谱搬移,数字滤波和抽取,实现数字下变频到基带;用FPGA实时控制,给ISL5416配置参数和系统时序控制。详细讨论了数字滤波器的设计和仿真。测试结果显示,系统动态范围大,镜像抑制比高,这是模拟中频接收机不具有的。整个系统集成度高,可靠性好,使用灵活,已在多个雷达产品中运用。

关键词:中频数字接收机;直接中频采样;数字下变频;数字滤波器

0 引 言

数字化接收机是软件无线电的重要内容,软件无线电的主要思想是将数字化推向前端,即将模数/数模转换器(ADC/DAC)尽量设在射频端,它是理想的软件无线电实现方法,也是数字化接收机的发展方向。早期的数字化接收机受模数转换器件(ADC)水平的制约,采用正交双通道零中频方案,即通过变频将射频变换到零中频(基带),正交解调得到模拟的正交信号,再进行数字化。由于该方案的主体变换都在模拟部分实现,数字化工作较少,不是真正意义上的数字化接收机。实现起来设备量较大,而且该方案中的正交混频器是模拟器件,得到的正交I,Q信号很难保证幅相正交精度。目前理论和实现上较成熟的数字化接收机方案是中频数字化接收机,即将射频信号经低噪声放大,经一次或二次下变频后,在中频(或高中频)直接采样,在数字下变频到基带得到正交的I,Q信号。目前,中频数字化接收机已在通讯、雷达上普遍使用。为适应灵活多样的模式,建立一个通用的中频数字化处理平台是十分必要的,现在有较高性价比的专用DSP芯片也为中频数字化接收机的实现提供了有力的硬件支持。ISL5416以其强大的可编程能力,使得中频数字化接收机的设计变得更为灵活和方便。本文即是采用专用DDC芯片ISL5416实现雷达中频数字化接收机的一例。该设计非常方便地在信号中频实现了数字化,而且可通过配置不同参数,实现不同模式、不同频率的接收和解调。

1 设计原理

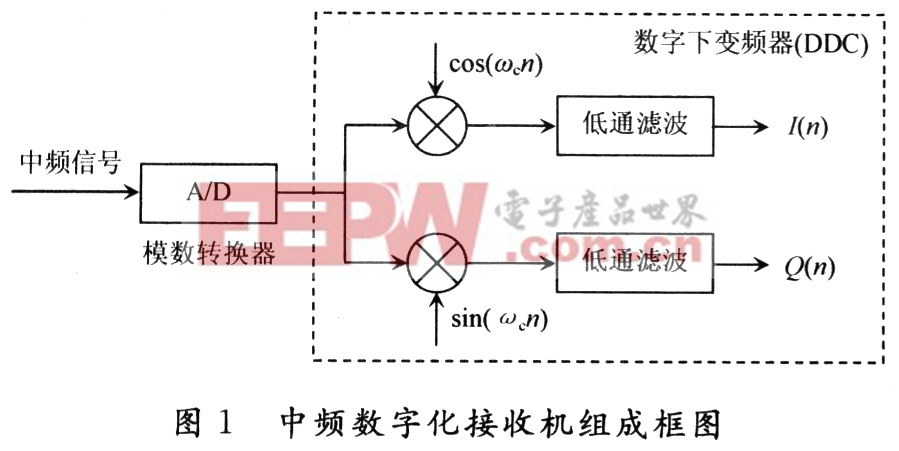

中频数字化接收机主要由模数转换器(ADC)、数字下变频器(DDC)组成,如图1所示。其中,A/D主要完成对模拟中频信号进行采样,得到数字化的中频信号,DDC将感兴趣的信号转换至基带,同时做抽样率变换及滤波处理,得到正交的I,Q信号送后续的数字信号处理器(DSP)进行基带信号处理。DDC是整个中频数字化接收机的核心,DDC由数控振荡器(NCO)、混频器、低通滤波器和抽取器组成。

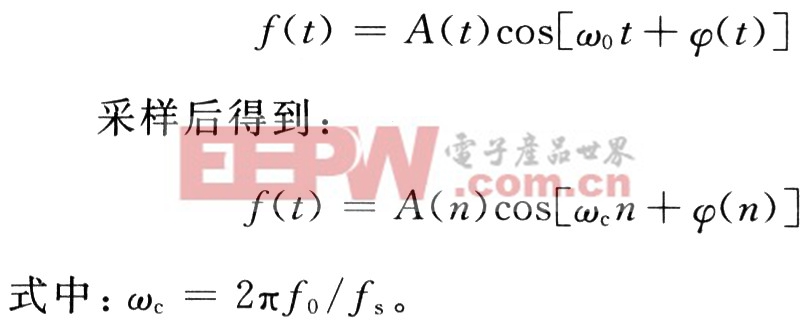

设输入模拟中频信号为:

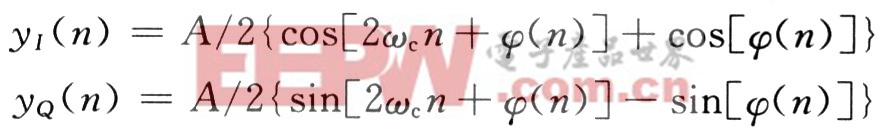

本地数字振荡器(NCO)产生的正交信号为:cos(ωcn)和sin(ωcn),与中频信号在混频器相乘后得:

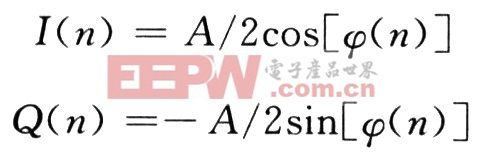

通过低通滤波器滤除倍频分量后,可以得到有用的正交I,Q信号:

由于信号的采样频率较高,也就是上式的I(n),Q(n)速率很高,一般远大于窄带信号的带宽,这时可对其进行速率转换(抽取),以降低此时的输出数据率。不过,抽取后的数据率应不小于信号带宽。在此之前,需经抗混叠滤波器滤波,以保证信号可靠完整地恢复。

图1中的中频信号是中频带限信号,如果此时中频信号的中心频率较低,可取高采样时钟过采样,依Nyquist采样定理,取采样率fs>2fH采样(fH为信号的高端),能够不混叠地恢复原信号。如果此时中频信号的中心频率较高,采样率与信号中心频率的关系不满足Nyquist采样定理条件,这时考虑是否满足带通信号的采样定理。这个定理是中频信号采样的理论依据,而Nyquist采样定理是带通信号采样定理的特例。带通采样定理:如果一个中心频率为fo频率带限信号,其频率限制在(fL,fH)内。

fo=(fL+fH)/2,当采样时钟fs与fo满足关系:

式中:n取能满足fs≥2B的最大正整数,B=fH-fL,则用fs进行等间隔采样,所得到的信号采样值能准确地确定原信号。

满足式(1)的中心频率为fo的信号经采样时钟fs采样后,f(t) 展开项中 cos(2 πfon/fs) 与sin(2πfon/fs)交替取值为零,当它们不为零时,取±1。可交替得到I,Q样值,不过这时的I,Q值已是经二分之一抽取,时域相差半个采样点,这时的I,Q值要在时间上对齐,符号修正,这样就很方便地实现了下变频。之后,只要将处理后的数据经数字滤波器滤波,按合适的抽取因子抽取就可得到所需的I,Q值。这种方法特别适合用FPGA设计的数字下变频器,不需要NCO,节省了设计数字混频器的逻辑资源,而且早期的商用数字下变频器件也是这种数字混频器,要求fo,fs满足式(1)的关系,如HARIS公司(现为Intersil公司)的HSP43216。

当信号中心频率fo较高,即是高中频信号时,用fs对信号采样属欠采样。当然fo,fs不一定严格满足式(1)的关系。fo,fs选用的总原则是从频谱上分析,采样后的信号经混频、滤波和适当抽取后,基带频谱没有混叠。本设计只是构建一个通用平台,以下的设计用采样率80 MSPS时钟采样,中频信号为中心频率10 MHz,带宽2 MHz,最后输出数据率2.5 MSPS。采样率和信号的最高频率满足过采样关系。

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- CMOS低噪声放大器中的输入匹配研究与设计(08-19)

- 实用的调频接收机电路设计(11-18)

- 意法半导体提升手机内部保护功能,为环保充电器开路(01-26)

- 如何收敛高速ADC时序(03-09)

- 低噪声、高线性度的3.5GHz LNA设计(08-14)