2×8低噪声InGaAs/InP APD读出电路设计

在红外通信的1 310~1 550 nm波段,高灵敏度探测材料主要有Ge―APD和InGaAs/InP APD,两者相比较,InGaAs/InP APD具有更高的量子效率和更低的暗电流噪声。In0.53Ga0.47As/InP APD采用在n+-InP衬底上依次匹配外延InP缓冲层、InGaAs吸收层、InGaAsP能隙渐变层、InP电荷层与InP顶层的结构。

APD探测器的最大缺点是暗电流相对于信号增益较大,所以设计APD读出电路的关键是放大输出弱电流信号,限制噪声信号,提高信噪比。选择CTIA作为读出单元,CTIA是采用运算放大器作为积分器的运放积分模式,比较其他的读出电路,优点是噪声低、线性好、动态范围大。

1 工作时序和读出电路结构

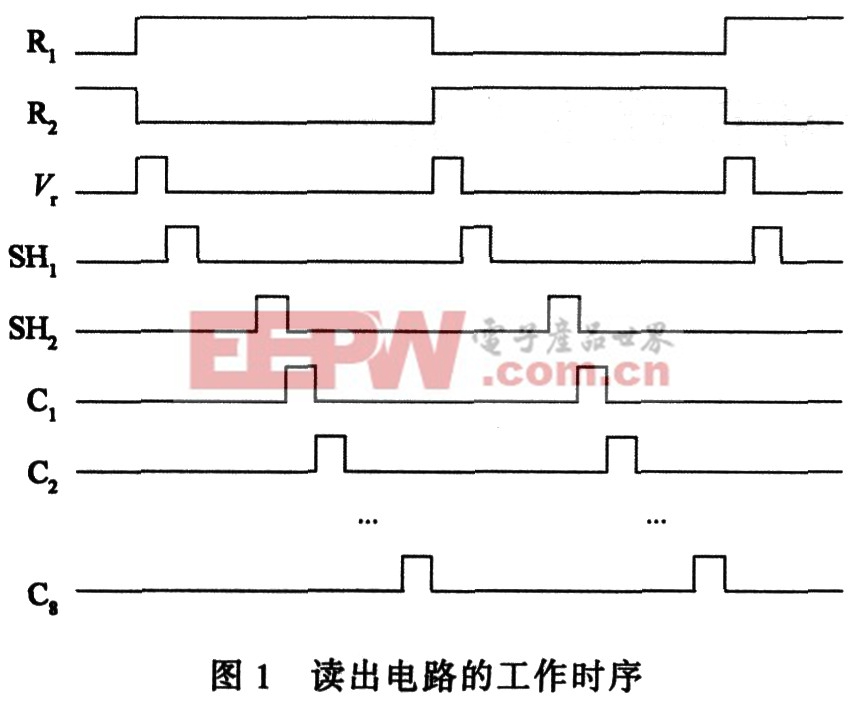

作为大阵列面阵的基础,首先研制了一个2×8读出电路,图1给出了该电路的工作时序,其中Rl、R2为行选通信号;Vr为复位信号;SHl、SH2是双采样信号;C1、C2、…、C8为列读出信号。电路采用行共用的工作方式,R1选通(高电平)时,第一行进行积分,SH1为高电平时,电路进行积分前采样,SH2为高电平时,进行积分结束前的采样,C1、C2、…、C8依次为高电平,将行上的每个像元上信号输出;然后R2为高电平,重复上面的步骤,进行第二行的积分和读出。

图2是2×8读出电路的结构框图,芯片主要由行列移位寄存器、CTIA和CDS单元组成,图中用虚线框表示:移位寄存器单元完成行列的选通,CTIA功能块将探测器电流信号按行进行积分,CDS功能块能抑制电路的噪声,如KTC(复位噪声)、FPN(固定图形噪声)等;FPGA主要产生复位信号(Vr)和采样信号(SH1、SH2),触发电路的复位和采样动作,C8为该组信号的触发信号,解决和芯片内行列选通信号同步问题。

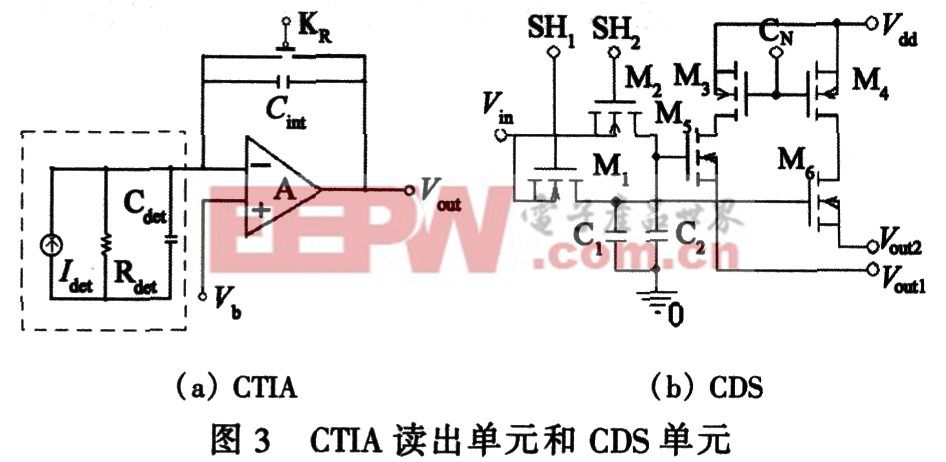

为了便于和读出电路的连接仿真,首先根据器件特性建立了器件的电路模型,如图3(a)中的虚线框所示,其中Idet、Rdet、Cdet分别表示器件的光电流、阻抗、寄生电容。图3(a)还给出了CTIA读出单元电路结构,主要由一个复位开关KR和积分电容Cint以及低噪声运放A构成。在CTIA结构中,设计一个高增益、低噪声、输入失调小、压摆率大的运放是确保读出电路信噪比高、动态范围大的关键。除此之外,积分电容Cint的设计也非常重要,在设计过程中发现,选择合适的积分电容也是关键之一。图3(b)是CDS单元,由采样管Ml、M2、采样保持电容C1、C2及M3~M6构成的差分器组成,Vin为CDS输入电位,也即CTIA的输出电位。Voou1和Vout2为两次采样输出,经过减法器后可以进行噪声抑制。

2 积分电容Cint

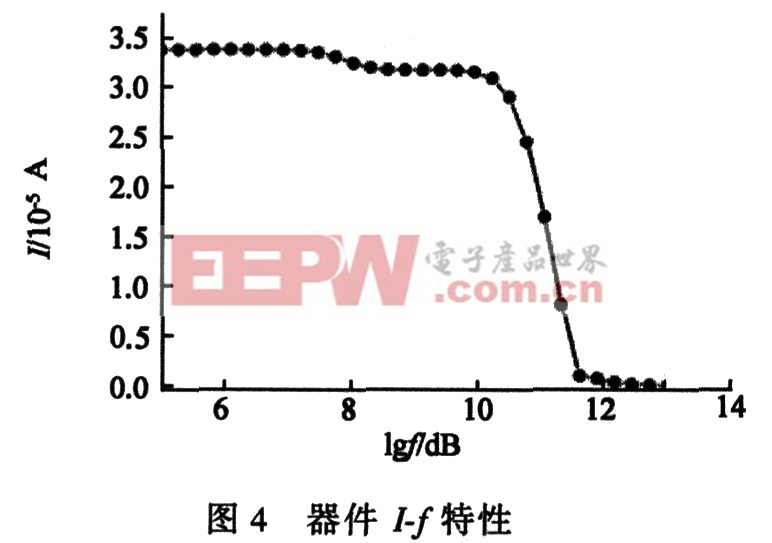

积分电容的设计主要和探测器信号电流的大小有关。图4是In0.53Ga0.47As/InP APD特性,仿真结果显示器件的工作电流一般在300 nA左右。

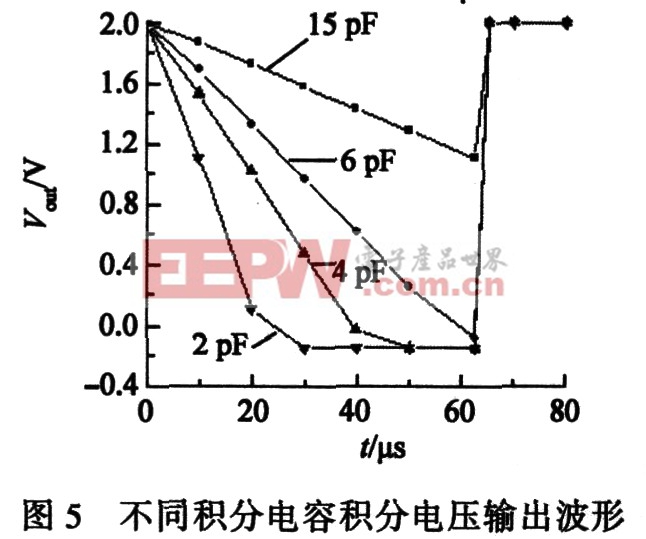

图5为器件电流取300 nA时积分电容分别为2、4、6和15 pF时的输出电压Vout的仿真结果。仿真参数设计:在器件厚度为20 μm的情况下,根据器件仿真结果进行计算,器件阻抗为2×109Ω,器件寄生电容为80 pF。参考电压Vb取2.0V,积分时间为60μs。可以看到对应不同的积分电容,积分电压到达饱和的时间是不一样的,也就是选择不同的积分电容,最佳积分时间是不一样的。如选用4 pF的积分电容,积分时间最好控制在40μs以下。

积分电容还决定电荷容量。电荷容量为

式中:Qm为电荷容量;Vref为参考电压,一般为1.5~3 V。式(1)表示增大积分电容Cint可以提高电荷容量。

在CTIA电路结构中,KTC噪声是最主要噪声,而KTC噪声也和积分电容有关。KTC复位噪声电压可以表示为

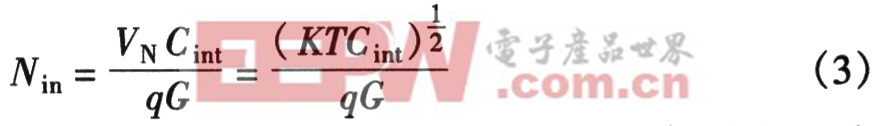

式中:VN为积分电容上复位引起的KTC噪声电压;K为波尔兹曼常数,其值为1.38×10-23J/K;T是绝对温度,取77 K。将此噪声电压折合成输入端噪声电子数,则表示为

式中:Nin为积分电容KTC复位噪声折合到输入端的噪声电子数;q为电荷常数,其值为1.60×10-19C;G为输出级增益。

图6表示了该噪声电子数和温度、积分电容Cint之间的关系。从图6可以看到,Nin随温度降低而减少,同时随Cint的增大而增多。所以在设计Cint时,必须兼顾探测器电流、积分时间、电荷容量Qm和KTC噪声折合到输入端电子数Nin,并且结合电路工作温度设计一个合适的值。在读出电路中,电容的工作温度为77 K,Cint设计为4 pF时,参考电压取2 V,电荷容量为8×10-12J。电路的输出级增益为O.65,KTC复位噪声折合到输入端的噪声电子数为768个,小于实际探测器的噪声电子数,而电荷容量也足够大,满足探测器读出的需要。在CTIA结构中,设计一个高增益低噪声的运算放大器。根据具体的应用合适设计。而开关管KR采用四管合抱管结构,减小导通电阻对电路的影响。图7为读出电路芯片的照片。

3 结论

电路采用O.6μm CMOS工艺流片,采用40脚的管壳进行封装,其中有效引脚为32个。用电注入法(恒流源模拟器件)测试了芯片的性能,电流信号为100~600 nA。功率耗散小于200μW。当积分电容为4 pF的时候,积分时间为36μs。时钟频率为0.5MHz的时候,一帧像元积分和读出的总时间为108μs。电路的电荷存储能力为5×107个,动态范围为l V左右,输出噪声为5.2×10-5Vrms。测试结果显示电路符合预期的设计要求。

- 采用MAX5026实现可编程APD偏置电路(03-19)

- 基于DS1875 SFP控制器的APD非线性响应补偿(12-05)

- APD非线性响应补偿(01-13)

- 高带宽实时示波器采用InP技术前端芯片组(11-22)

- CMOS低噪声放大器中的输入匹配研究与设计(08-19)

- 低噪声前置放大器电路的设计方法(03-10)