频率为700MHz~1GHz的FSK收发器芯片MICRF500的原理

时间:08-13

来源:互联网

点击:

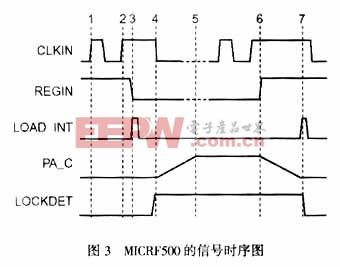

当CLKIN信号为高电平时,80位控制字首先读入移位寄存器,然后通过REGIN信号(正的或负的)装入并行寄存器。其接收和发射模式可由电路直接指定。图3所示是MICRF500中CLKIN、REGIN、内部LOAD、INT和PA-C信号的时序图。

图3中,在时序1时,倒数第二位数据被时钟信号装入移位寄存器(‘1’);在时序2时,最后一位数据被时钟信号装入移位寄存器(‘1’);时序3时,通过REGIN信号的转换可产生一内部装入脉冲,并将控制字装入并行寄存器,从而使电路进入新的模式(TX模式),并稳定在这种新模式。在时序4时,如果时钟信号变低,功放将慢慢开启以使RF输出信号最小。在PA开启前,PLL处于可靠的锁定状态。而在LOCKDET被设置后,PA开启。时序5时,功率放大器将满负荷开启。时序6时,一个新的控制字进入移位寄存器。当CLKIN为高时,REGIN信号发生跳变以关闭功率放大器。时序7时,功放关闭以产生内部装入脉冲,并将新控制字装入并行寄存器,从而使电路进入一个新的模式(节电模式),但CLKIN必须在产生内部装入脉冲后变低。当CLKIN为高时, REGIN上将不会出现跳变,此时,新的控制字在任何时间内,都不影响收发器操作,它将按照自己的方式按时进 入移位寄存器。

- AP3700的充电器系统解决方案(05-25)

- Vishay发布帮助客户进一步节约器件占位空间和系统成本的解决方案的视频教程(05-12)

- 为电源充电器和通用USB充电选择优化方案(09-24)

- MAX97003高效率H类耳机放大器的音频子系统(11-06)

- MAX78700 多通道隔离精密ADC(04-26)

- 基于MAX97002和H类耳机放大器的音频子系统(07-19)