频率为700MHz~1GHz的FSK收发器芯片MICRF500的原理

MICRF500是用于ISM(工业、科学和医药)和SRDC(短距离设备)的专用发射和接收芯片,其频率范围为700MHz~1GHz,采用FSK(频移键控)调制时的数据速率达128 kbauds,RF输出功率为10dBm,灵敏度为-104dBm,接收模式电流消耗为12mA,发射模式电流消耗为50mA,低功耗模式电流消耗 2μA。可广泛应用于遥测、无线控制、无线数据中继、无线控制系统、无线调制解调器和无线安全等系统中。

2芯片封装与引脚功能

MICRF500采用44-LQFP(BLQ)封装,各引脚功能如表1所列。

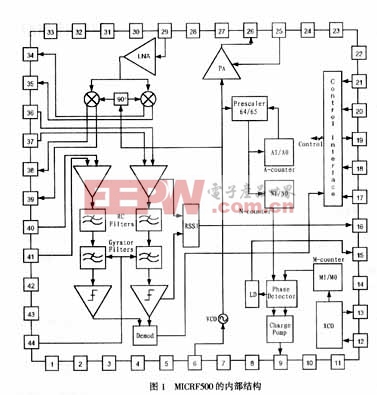

3内部结构与工作原理

MICRF500的内部结构如图1所示。该芯片内含接收、发射和控制接口(ControlInterface)三部分。其中接收部分由低噪声放大器(LNA)、混频器、RC滤波器(RCFilters)、解调器(Demod)、RSSI等电路组成。发射部分由功率放大器(PA)、预置比例分频器(Prescaler)、A计数器(Acounter)、N计数器(Ncounter)、M计数器(Mcounter)、压控振荡器(VCO)、相位检波器(Phase Detector)、充电泵(Charge Pump)、晶体振荡器(XCO)等电路组成。

当MICRF500处在接收模式时,PLL合成器产生本振振荡(LO)信号。N、M和A计数器给出的本振振荡频率被分别存储在NO、MO和AO寄存器中。由于接收器是零中频结构,因而用低功耗的集成低通滤波器作为通道滤波器。接收装置中的低噪声放大器(LNA)用于驱动正交混频器对。混频器输出馈送至两路相同的相位积分信道。每条信道包括前置放大器、三阶Sallet-Key RC低通滤波器和限幅器。主要信道的滤波器必须满足电路的选择性和动态范围。

Sallen-Key RC滤波器能通过编程划分成四个不同的截止频率:10kHz、30kHz、60kHz和200kHz。通过外围电阻可以调整滤波器的截止频率。解调器可解调I和Q信道的输出并同时输出一个数字信号。当检测I和Q信道信号的相对相位时,如果I信道落后于Q信道,FSK调制频率将位于本振振荡频率之上(数据 “1”)。如果I信道信号超前Q信道信号,FSK调制频率则位于本振振荡频率之下(数据“0”)。DATAIXO脚为接收器输出。RSSI(接收信号强度指示器)电路可用来显示收到信号的强度级别。两端的串行接口可用于对电路进行编程。VCO谐振电路、晶体、反馈电容和VCO的FSK调制元件、回路滤波器、功放和滤波器的偏置电阻等外围元器可用于RF输入输出的阻抗匹配和功率衰减。TX/RX的转换则可通过二极管来实现。

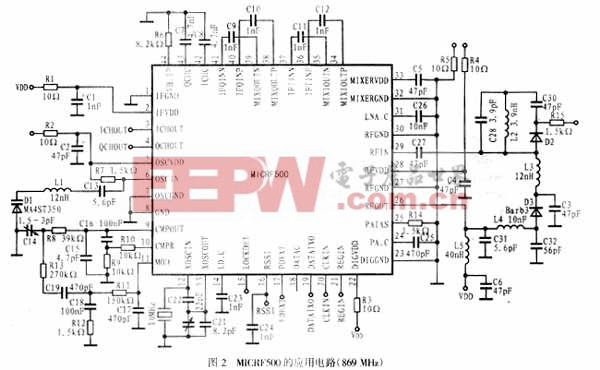

4应用电路设计

MICRF500的应用电路如图2所示,该电路的工作频率为869MHz。电路中,收发器的调制信号加到VCO,VCO和外围元件工作于869MHz。MA4ST-350-1141是MACON制造的一个专用变容二极管,而BAR63则是西门子公司生产的二极管。

由于VCO是一个基本的Colpitts振荡器,因而应有一个外部谐振器和一个可变电感,谐振器可由电感L1和线性电容C13组成。

晶体振荡器的晶振是RF输出频率的基准,因而要求具有很好的相位和频率稳定性。晶体振荡器通过调节可变电容C20可改变谐振频率。要获得小的频偏,晶体要预老化且要有小的温度系数。本设计采用10MHz晶振。

相位检测输出被转换成电压并经14脚(LDC)外电容C23的滤波后,产生的直流电压与位Ref0-Ref5设置的基准窗口相比较。 Ref0~Ref5为1时,基准窗口在0V;Ref0~Ref5为0时,其基准窗口的直流电压最大。另外,基准窗口能在两者之间线性步进地上升或下降。窗口的大小可等效为2个(Ref6=1)基准台阶或4个(Ref6=0)基准台阶。

实现FSK有三种方法:第一种是使用VCO实现FSK调制,其对应的发射频率将被编程在分频器A1、N1和M1中。在TX模式,DATAIXO端保持在三态,直到开始发射数据;第二种是通过开关在A、N和M分频器两组之间实现,A、N和M值对应到接收频率和两发射频率。发射数据“0”时,将对分频器 A0、N0和M0进行编程;发射数据“1”时,将对分频器A1、N1和M1进行编程;第三种则可通过加/减1到分配器A1来实现,其频偏与比较频率相等,发射频率的校准可通过对A1、N1和M1进行编程来实现。所有类型的FSK调制数据都从引脚端DATAIXO输入。

回路滤波的设计对优化参数是很重要的,如调制速率、PLL锁定时间、带宽和相位噪声等。低位率通常可调制在PLL内,而将回路锁定在不同的频率上则可通过开关分频器(M、N和A)来实现。高调制率(超过2400bps)一般靠PLL外调制来实现,设计时通常直接加到VCO。此时,回路滤波器的值可通过软件进行编程确定。

发射功率放大器是基本的AB类,最后一级是开集电极(OC)电路,因此应外接一负载电感(L2)。放大器的直流电流通过外接偏置电阻R14来调整。当偏置电阻值为1.5kΩ时,偏置电流为50μA。最后一级电路的偏置电流大约为15mA。

阻抗匹配与天线的类型也有很大关系,设计时可采用最大输出功率,并在功率放大器上接一约100Ω的阻抗。输出功率可编程为8级,每级大约相差3dB,可以通过控制字Pa2-Pa0来进行控制。

为了预防干扰信号干扰功放,功放应当缓慢的导通和截止。通过连接到24脚的电容C25可使偏置电流在限定范围内上升或下降。上升/下降电流典型值为 1.1μA,当电源为3V时,开关速率为2.6μs/pF。由于转换功放开关会影响PLL,所以开关速率必须与PLL带宽相对应。

缓冲放大器通常连接到VCO和功率放大器之间。功率放大器的输入信号可以放大到期望的输出功率。通过设置位Gc为“0”可以旁路缓冲级。

RF接收器的低干扰放大器可利用提升输入信号来优化频率转变过程。其主要目的是为了预防混频器干扰。LAN是一个两级放大器,正常时,在900MHz 处可以获得23dB的增益,LAN具有一个直流外馈环,可为LAN提供偏置。外接电容C26对所有的直流反馈环路均可起到退耦和稳定作用。

通过设置ByLAN位为“1”可以旁路LAN,这对强信号是非常有用的。

混频器在900MHz有12dB增益,在34、35和38、39脚中,每一路混频器的输出阻抗约为15kΩ。

解调器解调出来的信号的频偏必须永远比频漂大,且至少等于波特率加上频漂。

限幅器是一个零点检波器,其输出为与I-Q相位差相对应的值,波形是边缘陡峭的方波。

解调器的作用是解调I和Q信道输出并产生数字量输出,同时可用来检测I和Q信道信号之间的相位差。对于I信道,在限幅器输出的每一个边沿(上升沿和下降沿),Q信道限幅器输出的振幅均被采样,反之也如此。解调器的输出通过DATAIXO引脚来实现。数据输出被IF信号每周期更新四次。如果I信道信号滞后于Q信道,FSK调制频率将位于LO频率上方(数据“1”),而如果I信道超前Q信道,则FSK调制频率将位于LO频率下方(数据“0”)。

解调器的输入和输出通过一阶RC低通滤波器滤波并经过斯密特触发器放大来产生方波。在低位率时,增加引脚18的电容(DATAC)可以减少RX数据信号滤波器的带宽。滤波器的带宽必须根据位率来进行调整,这个功能一般通过RXFilt位来控制。

RSSI(接收信号强度指示)电路的输出与代表RF输入信号强弱的直流电压相对应。当接收到的RF输入信号使RSSI输出增加时,RSSI将作为信号的有无指示器而用于唤醒电路。无信号时,电路将处于睡眠模式以长电池寿命。

在编程时,可用两线(CLKIN和REGIN)式总线来编程电路,两线串行总线接口可以控制分频器、选择TX的功率和RX以及合成器电路功能块,其接口由一个80位编程寄存器组成。数据和第一有效位从REGIN线进入,第一位输入为P1,最后一位输入为P80。程序寄存器中的位安排如表2所列。

- AP3700的充电器系统解决方案(05-25)

- Vishay发布帮助客户进一步节约器件占位空间和系统成本的解决方案的视频教程(05-12)

- 为电源充电器和通用USB充电选择优化方案(09-24)

- MAX97003高效率H类耳机放大器的音频子系统(11-06)

- MAX78700 多通道隔离精密ADC(04-26)

- 基于MAX97002和H类耳机放大器的音频子系统(07-19)