基于DDS技术的杂散分析及抑制方法

频率分量。

3 改善DDS杂散的方法

全数字结构给DDS带来输出带宽和杂散的不足。目前,降低DDS输出杂散的方法主要有以下几种:

3.1 采用抖动注入技术

由前面的分析可知,相位截断误差给输出信号引入了周期性的杂散,因此设法破坏杂散的周期性及其与信号的相关性,可以有效地抑制相位截断带来的误差。抖动注入技术是基于打破相位截断误差周期性的原理工作的,采用抖动注入后的杂散抑制可达到与增加2bit相位寻址相同的效果。抖动注入采用加入满足一定统计特性的扰动信号来打破误差信号序列周期性,将具有较大幅度的单根杂散信号谱线的功率在较宽的频率范围内进行平均来改善总的信号频谱质量。根据抖动注入的位置不同,可有频率控制字加扰、R0M寻址加扰、幅度加扰,根据抖动注入的误差对象不同,由相位截断误差加扰和幅度量化误差加扰。C.E.Wheatly提出了一种针对相位截断误差的抖动注入方法,在每次累加器溢出时,产生一个随机整数加到累加器上,使相位累加器的溢出随机性的提前,从而打破周期性,抑制了杂散,但增加了背景噪声。

3.2 ROM幅度表压缩

DDS是通过查表将相位转换为幅度值,如果能够将幅度表进行压缩就相当于增加了R0M数据寻址位数,DDS输出频谱将进一步得到改善。各国学者对此进行了研究并提出了各种压缩算法,利用三角函数的恒等变换,将一个大的R0M分成几个小R0M,通过逻辑控制电路实现对sin 的近似。还可以利用弦信号的波形具有四分之一对称性,R0M表中只需存储[0,丌/2]的波形,在电路中利用相位的最高位控制输出波形的符号,次高位控制 R0M表的寻址,对相位和幅度进行适当的翻转便可得到整周期波形,R0M表压缩比4:1。在成功压缩了R0M表的同时也带来了一些缺点,如逻辑控制电路复杂、实时性下降等。

3.3 PLL+DDS法

如前所述,DDS技术具有频率分辨率高,频率捷变速度快,变频相位连续等优点,但带宽和杂波抑制较差,而PLL频率合成技术具有宽带、高频率、频谱质量好,对杂散抑制较强等优点,但其频率捷变速度较慢。所以,在一些信号捷变速度、带宽,频谱质量要求相对折中的电路中,结合PLL频率合成技术与DDS 技术的结合,将是一种解决DDS杂散的理想解决方案。

3.3.1 PLL+DDS频率合成原理

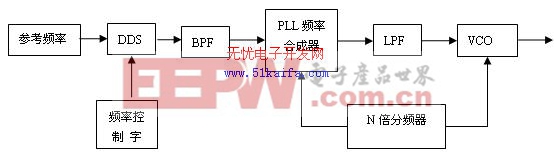

将DDS技术和PLL频率合成技术结合起来,用一个低频的DDS源激励一个PLL系统,用PLL环路将DDS信号倍频到高频信号,用滤波器滤除DDS输出信号杂波干扰,从而使系统同时具有锁相环技术和DDS技术的优点,使输出的信号满足电路的需要。系统组成如图2所示

图2

3.3.2 PLL+DDS频率合成器中的杂散抑制

当DDS源驱动PLL锁相环时,因为PLL锁相环相当于一个高Q值的跟踪滤波器,其带宽一般不大于100KHz,所以DDS中的大部分杂散会被抑制的很好,从而DDS输出信号中的杂散偏离主谱线距离大于锁相环路带宽的杂散不会恶化。在PLL+DDS系统中,应根据DDS的原理选择适当的时钟频率和输出信号频率,使DDS输出信号与边端的杂散处于相对理想状态,从而提高了系统的频谱纯度。

3.3.3 PLL+DDS频率合成器的实现

PLL+DDS频率合成器的组成如图3所示,下面介绍所选用的主要器件:

1. DDS部分

选用AD公司的AD9852高度集成化芯片,它采用了先进的DDS技术,结合内部高速、高性能D/A 转换器和比较器,形成可编程、可灵活使用的频率合成功能。当提供给AD9852精确的频率时钟源时,AD9852将产生高稳定、可编程频率相幅的正弦波。 AD9852使用先进的CMOS技术,使得提供给这个高性能芯片的工作电压仅为3.3V。

2. PLL合成器部分

PLL合成器部分采用AD公司的ADF4106,它主要由低噪声数字鉴相器、精确电荷泵、可编程分频器、可编程A、B计数器及双模牵制分频器等部件组成。数字鉴相器用来对R计数器和N计数器的输出相违进行比较,然后输出一个与二者相位误差成比例的误差电压。鉴相器内部还有一个可编程的延迟单元,用来控制翻转脉冲宽度,这个脉冲保证鉴相器传递函数没有死区,因此降低了相位噪声和引入的杂散。

图3

4 结束语

直接数字频率合成(DDS)是一种新型的频率合成技术,它代表了频率合成技术数字化发展的新方向。但是,DDS所固有的杂散和噪声,并且在频率升高时杂散和噪声也随之增加,使它的应用范围有一定的限制。所以如何减少DDS输出中的杂散和噪声成分是当今DDS研究中的核心问题之一。本文所介绍的抖动注入技、平衡DAC结构以及关于ROM幅度表压缩的几种算法,都能有效地减少DDS输出信号中的杂散。尤其当要求得到既有高的频率分辨率,又有较快的转换速度和较低噪声的高频甚至微波信号时,DDS+PLL技术就显现出了较强的优越性,经过实际的工

- 一种基于AD9857的信号发生器的设计(09-07)

- 基于FPGA及DDS技术的USM测试电源的设计 (09-08)

- 高性能双通道DDS芯片AD9958及其应用(02-04)

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 基于DDS的调频信号发生器的设计与仿真(04-12)