基于FPGA的DDS信号发生器设计

4 系统功能仿真和验证分析

4.1 频率控制字生成模块仿真与分析

频率控制字的生成直接影响着波形数据的寻址,该模块负责快速记录并实时显示输入的频率数字,准确计算得到相应的频率控制字。系统键盘为高速动态扫描(频率为200Hz),采用状态机设计,设置了按键去抖动功能。在FPGA开发平台对该模块进行功能验证,整体无误操作产生,几乎没有时滞效应,按键的防抖动效果也良好,达到了预期的目的。

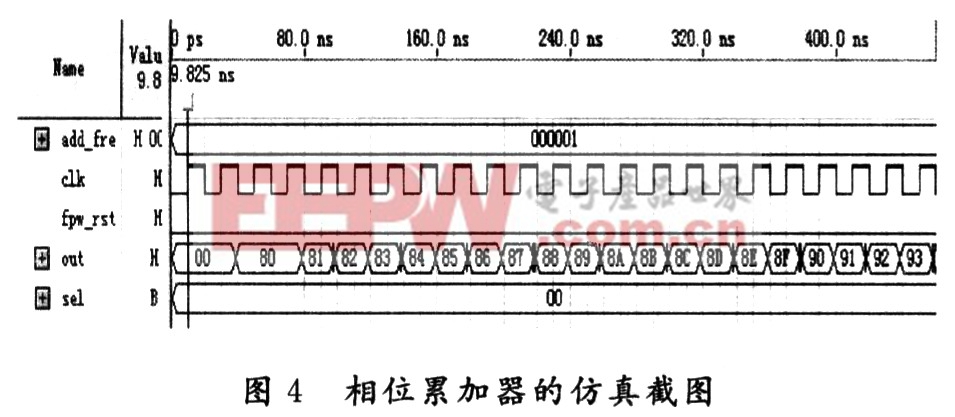

4.2 相位累加器模块仿真与分析

相位累加器用于实现相位累加,并存储其累加结果。当前,相位累加器的值和时钟周期到来后的相位累加器的值相差k(k为频率控制字)。该模块的仿真波形如图4所示。

4.3 实验波形观测与误差分析

信号发生器功能验证无误,用示波器观测实验波形如图5所示。

检测输入频率为0~10 MHz时,波形形状均良好,未出现明显失真。计算理论误差为0.095%,在实测中发现,波形数字的误差相对很小,不足0.1 %。由于滤波整形电路存在高频耦合通路,产生线间串扰,对滤波效果形成了不利影响,因此滤波器设计必须满足频带宽,截止特性好,抗干扰性强等特性。

5 结 语

介绍了以直接数字频率合成技术(DDS)为基础的波形信号发生器工作原理和设计过程,并在FPGA实验平台上设计实现了满足各功能指标的信号发生器。系统硬件除需外加滤波整形电路外,其余部分均可在FPGA开发实验系统KH-310上集成开发,系统软件可在Quartus下编写代码,实现数据信息处理和控制操作等功能。整体开发环境成熟,应用工具齐全,随着FPGA性价比的不断提高,基于FPGA平台开发信号发生器将逐步走向标准化、规模化和产品化。

现代电子和通信技术的发展,对信号发生器提出了更高、更严格的要求。除了对信号频率范围、带宽和频率分辨率的严格限制外,对信号的波型及调制特性等也有着苛刻的规定。研究和开发具有更高性价比的信号发生器将是当前和今后一段时间内亟需解决的课题。这里旨在建立一种基于FPGA的简单数字信号发生器设计方法。若能充分利用FPGA强大的数据运算处理能力以及编程灵活、运行速率快等优点,合理整合IP核资源和SoPC技术,简化设计结构,一定可以设计出功能多样、性能更加出色的信号发生器。

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)