高速数字记录系统中光纤下载卡的逻辑设计

FIFO接口,设置此FIFO的目的有两个:一是时钟域转换,外部输入的主时钟为125MHz,而RocketIO采用32位模式,在2.5Gb/s的速率下,逻辑的主工作时钟为62.5MHz。而ping64模块采用PCI总线提供的PCI66MHz时钟。两者时钟不在同一个时钟域,所以用异步FIFO将时钟域隔离。二是数据的缓存。根据FIFO的almost full信号产生反压信号,送交RocketIO,使对端收到反压信号后,停止发送数据。

所用Xilinx的RocketIO核其实为aurora 核,这是一个双向串行数据通信链路控制器,能将反压信号随数据一起发往对端。其接口相对简单,有两种模式,一种是帧模式,另一种是流模式,可以根据应用灵活选择。在本项目中采用的是帧模式。

主DMA处理的软硬件流程

在DMA处理中,采用内存乒乓操作来提高系统的吞吐量。软件中的驱动采用Windriver开发,其工作主要分三部分。

1 初始化,包括申请内存,配置DMA列表,配置DMA相关寄存器,启动逻辑开始工作。

2 中断处理函数。在此函数中,屏蔽中断,并启动DPC处理。

3 DPC(延迟过程调用),根据逻辑提供的状态标识,将相应的内存块的数据搬移至硬盘中,然后取消中断屏蔽,复位状态标识,使系统可以接收下一个中断。

数据的搬移不在中断处理函数中完成,是由于中断处理函数具有较高的优先级,如果将耗时的数据搬移放在这里进行,会明显降低系统的响应时间。而DPC的优先级在所有的外部中断之下,不会因此而降低对其他外部中断的响应速度。

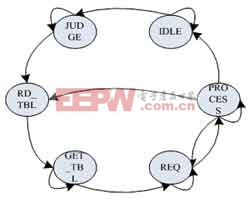

主DMA逻辑的主要工作是读取驱动配置的DMA列表,根据列表中的内存地址和长度,对内存进行主DMA写操作。操作完成后,通过置位状态标识,通知驱动来读取数据。状态机转移如图4所示。

图4 DMA主状态机转移图

● IDLE状态:在此状态下,等待软件的使能信号。使能信号有效则进入JUDGE状态,否则等待。

● JUDGE状态:在此状态下,判断乒乓标志。根据乒乓标志决定本次处理应该选择哪一个内存块。

● RD_TBL状态: 发出读DMA列表的地址信息。然后进行GET_TBL状态接收列表数据。

● GET_TBL状态:在此状态下,读取DMA列表数据,并将列表中的内存地址和长度信息写入相应的寄存器中。然后进入REQ状态。

● REQ状态:在此状态下,对异步FIFO的空信号进行判断。如果非空,则进入PROCESS状态,否则在REQ状态等待。

● PROCESS状态:在此状态下,进行数据传输。由于PCI主DMA对burst长度有限制,当传输完预定长度的数据后,首先对本次长度进行判断。如果未完则进入REQ状态等待,否则判断本列表是否最后一个列表。如果是,则进行IDLE状态。否则进入RD_TBL状态读取下一条DMA列表表项的数据,继续处理。

- 高速数字电路电源系统的电磁兼容研究(11-20)

- 资深工程师技术笔记:谈谈高速数字系统的滤波电容(04-08)

- 基于凌华PCI-9846高速数字化仪的复杂超声场自动检测与分析(三)(11-28)

- 基于凌华PCI-9846高速数字化仪的复杂超声场自动检测与分析(二)(11-28)

- 3 种高速数字电路隔离技术(09-06)

- 基于PXI的高速数字化仪模块(09-10)