克服放大器电气过应力问题(上)

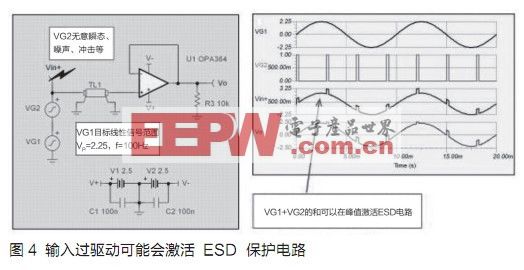

电路的例子。低频信号VG1表示来自变送器输出端的信号。该变送器远离放大器,有一条线缆(TL1)将它们连接起来。该电路中,周围环境使线缆上出现了瞬态。 VG2是与变送器输出信号(VG1)结合在一起的计划外瞬态信号。总信号振幅超出了放大器的最大规定输入范围。一个足够强的瞬态信号将会触发运放输入ESD电路。 位于该放大器非反相输入端前面的电阻限制了产生输入电流的大小。ESD单元设计旨在极短的时间内安全地传导数安培电流,该传导持续时间不超过几十到数百纳秒。当ESD单元在EOS事件期间激活时,电流传导的时间取决于EOS脉冲或过压特性。这些相同的ESD单元一般可持续处理5~10mA的电流,当占空比下降时可持续处理的电流安培数会大大增加。在这些条件下,它们可能非常安全并且不受过压的影响。 参考文献 [1]SPICE-Based Analog Simulation Program[R/OL]. http://focus.ti.com/docs/toolsw/folders/print/tina-ti.html [2]OPA364[R/OL].http://focus.ti.com/docs/prod/folders/print/opa364.html [3]OPA374[R/OL]. http://focus.ti.com/docs/prod/folders/print/opa374.html [4]OPA227[R/OL]. http://focus.ti.com/docs/prod/folders/print/opa227.html [5]Kuehl T.Using the infinite-gain, MFB filter topology in fully differential active filters[R/OL]. http://focus.ti.com.cn/cn/lit/an/slyt343/slyt343.pdf [6]Baker B. A Baker's Dozen: Real Analog Solutions for Digital Designers[M]. Newnes,2005

TI 运算放大器 运放 EOS 电气过应力 ESD 201004 相关文章:

- DPA-Switch为应对PoE受电设备设计挑战提供有效解决方案(11-06)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 用LatticeXP FPGA 桥接吉比特媒体独立接口(01-18)

- 单片机与串行AD转换器TLC0834的接口设计(01-22)

- 8位高速A/D转换器TLC5510的应用(02-16)

- 改善平板显示器的音频性能(02-13)