一种低功耗高速的跟随器设计和实现

时间:04-16

来源:互联网

点击:

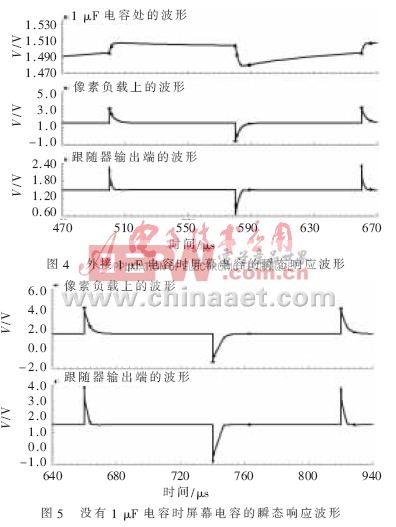

由上可见,该高速跟随器在2种不同负载电容的情况下均能满足系统要求。在实际应用中,可考虑去掉1 μF的片外电容,从而节省芯片成本和FPC面积。本设计中,CSTN-LCD系统要求跟随器面积为600 μm×100 μm。

低功耗、高速跟随器的设计一直是制约LCD驱动芯片中的瓶颈。本文通过采用辅助充放电运放的方案,设计出一种低功耗、高速的跟随器,也有利于进一步优化芯片面积与成本,因此具有广阔的应用前景。

- RS-485网络设计降低功耗问题(01-26)

- 低功耗CMOS电压基准源的设计(08-27)

- 一种新型低功耗两级运算放大器的实现(01-20)

- 创建理想的低功耗设计(01-14)

- 新一代电池供电装置的超低功耗设计(07-18)

- 基于绝热逻辑的低功耗乘法器电路设计(07-23)