采用PLL(锁相环)IC的频率N(1~10)倍增电路

电路的功能

很多电路都要求把频率准确地倍增,使用PLL电路可很容易组成满足这种要求的电路。例如主振频率为1KHZ,若使用倍增器内插10个脉冲,可变成10KHZ的脉冲信号。在VCO中,即使主振频率发生变化,也能获得跟踪主振荡频率的倍增频率N.F0,这是本电路的一大特点。

电路工作原理

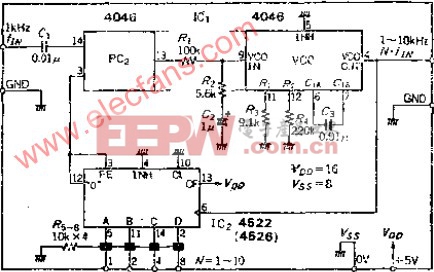

具有PLL主要功能的C-MOSIC4046是一种最高工作频率为1MHZ的集成电路,将其与可编程除法器连接,便可构成把输入频率递增N倍的电路。相位比较器PC2是检查FIN与N分步器输出的频率、相位是否相等的电路,它输出0~VP-P的信号,经环跑滤波器滤波后对VCO的振荡频率进行控制,VCO的可变范围FMAX~FMJA就是从输入频率FIN到N.FIN。考虑到电路的误差和长期稳定性实际上增加了若干安全余量。

在实际应该中不一定局限限于本电路。下面介绍一下设计顺序:

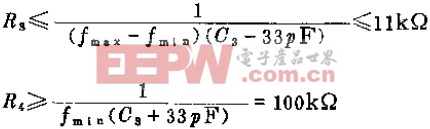

如果N=1~10,VCO的振荡频率为1KHZ~10KHZ,若C3=0.01UF,则:

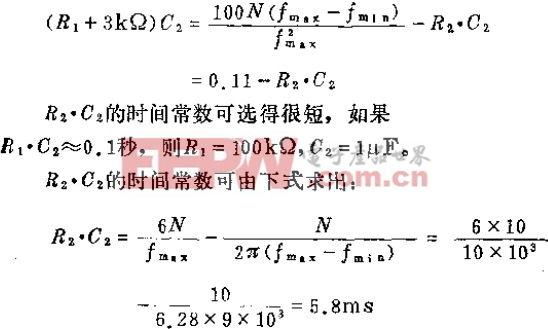

按此计算,VCO的控制电压范围没有余量,不能进行正常工作。为此,决定FMIN值的RS应具有20%的安全余量,基计算值为8.8K现取9.1K,因为VCO的控制电压很小,所以FMTN应有50~100%的安全余量,并把最小控制电压设计得稍高一点,R4取180~220K,环路滤波器决定PLL电路的频响,用由R1和C2确定的时间常数分段,N=10时。

因为C2为1UF,所以R2=5.8*10的次方/10的次方=5.8K。

PC2的输入电阻为1M,即使FC=100HZ,输入电容器C1的容量也可取1600PF以上,这里取0.01UF,上述计算结果是大概的。

调整

PLL电路工作正常与否,可采用下述办法进行检查:N在1~10范围内改变,如果VCO的控制电压成阶梯状上升,则表明工作正常,如果工作不正常,可把VCO单独断开,从引线9输入0~5V电压,检验VCO在FMIN以下,FM0X以上的频率是否发生振荡。

应用要点

可编程分频器的分频比如取10以上,便可获得更大的倍增率,但须串联2~3个计数器IC。

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 全数字锁相环的设计及分析(03-01)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环中YTO自校准技术的应用(10-02)

- 基于DDS+PLL技术的频率合成器的设计(07-23)

- 锁相环在反馈电路上的应用(01-10)