高压功率VDMOSFET的设计与研制

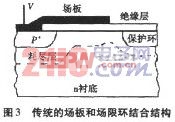

本文研究的新型结终端结构(如图3所示),是采用场板覆盖保护环的方式,避免了传统场板与场限环结构的设计难题,而使其简单化。

这种结构在版图设计上通过增加铝场板的长度来实现,比较容易控制,使得金属覆盖过离主结最近的场限环,它不仅起到了场板和场限环的效果,又避免了传统结构在场板的边缘产生新的电场峰值,避免了电压在场板边缘和场限环之间的提前击穿。

4 仿真优化结果

本设计采用“5个场限环+铝场板+多晶场板”的终端结构,通过工艺仿真软件TSUPREM-4和器件仿真软件MEDICI进行联合仿真,不断调整工艺参数,优化元胞和结终端结构,最终使各项参数的仿真指标满足设计要求(详见表1)。

5 器件研制结果分析

本产品研制按照功率VDMOSFET正向设计的思路,选取100>晶向的衬底硅片,采用硅栅自对准工艺流程,首次流片遵照计算机仿真优化的工艺条件,进行工艺摸底;针对测试结果,逐步进行局部工艺调整,最终使得产品指标满足设计要求。

(1)第一次流片

产品测试结果表明:产品的击穿电压均值为438.82 V,并且普遍低于设计要求的500 V。

经分析,其可能存在的原因是:由于衬底反扩散较大,从而导致外延层电阻率偏低,使得击穿电压降低。因此,在第二次流片时,将外延电阻率提高5 Ω·cm,其它工艺条件保持不变。

(2)第二次流片

测得的击穿电压平均值551.68 V,大于500 V,满足设计要求。然而,随着外延层电阻率的提高,部分导通电阻已大于设计要求的850 mΩ。

改进方案:对于高压功率VDMOSFET器件,JFET电阻在导通电阻的组成部分中,占有相对较大的比重。因此,在击穿电压余量充分的条件下,可考虑通过适当减小P-body推结时间的方法,从而增加两相邻P-body的间距,降低JFET电阻。因此,在第三次投片时,将P-body的推结时间调减20分钟,其它工艺条件相对于第二次流片保持不变。

(3)第三次流片

测试结果表明:在减小P-body推结时间后,导通电阻小于850 mΩ,满足设计要求;虽然产品的击穿电压(均值536 V)有所下降,但仍满足大于500 V的设计要求;其余静态参数、动态参数指标也均满足设计要求。

因此认为,本文高压功率VDMOSFET的器件设计与研制工作是成功的。

6 结束语

本文在计算机仿真优化的基础上,通过对产品测试结果的分析及工艺条件的调整,最终实现了成功研制。相对于传统的流水线小批量投片、反复试制的方法大大节约了研制成本,收到了事半功倍的效果。

随着半导体生产制造工艺的不断改进,器件模拟和工艺模拟的精度与实际工艺流程的吻合性将越来越好,使产品的模拟结果更具有实用性、可靠性。

VDMOSFET 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)