高压功率VDMOSFET的设计与研制

摘要:按照功率VDMOSFET正向设计的思路,选取(100)晶向的衬底硅片,采用多晶硅栅自对准工艺,结合MEDICI器件仿真和SUPREM-4工艺仿真软件,提取参数结果,并最终完成工艺产品试制,达到了500 V/8 A高压、大电流VDMOSFET的设计与研制要求。结果证明,通过计算机模拟仿真,架起了理论分析与实际产品试制之间的桥渠。相对于原来小批量投片、反复试制的方法,不仅节约了时阍,降低了研制成本,而且模拟结果与实际试制结果之间能够较好地吻合。针对传统结终端结构的弊端,提出了一种新型结终端结构,大大提高了产品的击穿电压和可靠性。

关键词:功率VDMOSFET;计算机模拟仿真;结终端结构

O 引言

随着现代工艺水平的提高与新技术的开发完善,功率VDMOSFET设计研制朝着高压、高频、大电流方向发展,成为目前新型电力电子器件研究的重点。

本文设计了漏源击穿电压为500 V,通态电流为8 A,导通电阻小于O.85 Ω的功率VDMOSFET器件,并通过工艺仿真软件TSUPREM-4和器件仿真软件MEDICI进行联合优化仿真,得到具有一定设计余量的参数值。最后在此基础上进行生产线工艺流片,逐步调整部分工艺条件,最终实现研制成功。

1 VDMOSFET工作原理

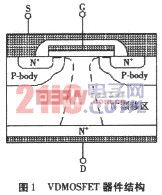

VDMOSFET是电压控制器件,在栅极施加一定的电压,使器件沟道表面反型,形成连接源区和漏区的导电沟道。基本工作原理如图1。

当栅源电压VGS大于器件的阈值电压VTH时,在栅极下方的P型区形成强反型层,即电子沟道,此时在漏源电压VDS的作用下,N+源区的电子通过反型层沟道,经由外延层(N-漂移区)运动至衬底漏极,从而形成漏源电流。

当VGS小于阈值电压VTH时,栅极下方不能形成反型层沟道。由于外延层(N-漂移区)的浓度较低,则耗尽层主要在外延层(N-漂移区)一侧扩展,因而可以维持较高的击穿电压。

2 参数设计

2.1 外延层电阻率和厚度

外延层的电阻率ρ越大(掺杂浓度Nepi越小),则器件的击穿电压越大。然而,导通电阻Ron也相应增大。因此,在满足击穿要求的前提下,ρ越小(Nepi越大)越好;而从导通电阻的角度考虑,又限定了该电阻率的最大值。所以将在计算机仿真过程中,调整P-body的注入剂量、推阱时间和外延层电阻率、厚度,得出最佳的结构参数。

2.2 阈值电压

影响阈值电压的因素主要是P-body浓度NA,栅氧化层厚度tox和栅氧化层的面电荷密度Qss,主要通过调整P阱注入剂量和推阱时间来调节阈值电压Vth。

此外,栅氧化层厚度tox受栅源击穿电压的限制,tox≥VGS/EB,SiO2的临界电场EB一般为5×106~107 V/cm;由此算得tox的值为30 nm~60 nm;由于P-body为非均匀掺杂,VTH难于用公式准确计算,因此栅氧化层厚度tox和pbody浓度的最佳值需借助于计算机仿真优化来确定。

2.3 导通电阻

对于功率VDMOSFET器件,在不同耐压下,各部分电阻占导通电阻的比例是不同的。对于高压VDMOSFET器件,漂移区(外延层)电阻RD和JFET区电阻RJ是主要的。

因此,本设计在满足耐压的情况下,采用穿通型结构,以减小外延层厚度,并适当增加JFET区的宽度,从而减小RD与RJ。

2.4 开关时间

优化开关时间的方法包括两个方面:减小多晶硅栅的电阻RG和减小输入电容Cin。在输入电容中,密勒电容CGD是主要的影响因素。

减小多晶硅的电阻RG可以在工艺过程中提高多晶硅的掺杂剂量,在版图设计过程中增加栅极多晶硅与栅极铝引线的接触孔;减小输入电容Cin主要是减小密勒电容CGD,即要增加栅氧化层厚度tox,这会加大阈值电压VTH,因而需要折中考虑。

3 横向结构设计

3.1 元胞结构选取

由于正三角形元胞的电场容易集中,导致漏源击穿电压的降低;六角形元胞的对角线与对边距的比值为,小于方形元胞的对角线与边长的比值,电流分布的均匀性好,曲率效应小;圆形元胞牺牲率(即A’/Acell,其中A’为元胞边缘结合处电流不能流过的无效区面积,Acell为元胞总面积)大于六角形元胞。

因此,本文所设计的500 V高压VDMOSFET器件采用正六角形“品”字排列的元胞结构。

3.2 栅电极结构

功率VDMOSFET由很多小元胞单元并联组成。而由于栅极多晶硅电阻的存在,使得在一定的栅极偏压下,离栅极压焊点较远的元胞沟道不能充分开启。因此,为了降低栅电极材料电阻的影响,通常将栅极压焊点处的金属引伸到离压焊点较远的元胞单元处。本文所设计的功率管从压焊点处引伸3条金属条并与下面的多晶硅相接触。

3.3 结终端结构设计

传统的场板与场限环相结合的结终端结构如图3所示。设计时,如果场板和保护环的间距过大,场板下的耗尽层扩展到保护环之前PN结就首先击穿,保护环将起不到作用。

VDMOSFET 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)