ADS1282及其在单通道地震数据采集单元中的应用

数据采集系统中的采集信号质量很大程度上取决于模数转换器的选取及使用。为满足高精度地震数据采集的应用需要,设计一种高集成度、单通道地震数据采集单元,该单元可实现单道地震信号的拾取、数据转换、存储及数据传输功能,采用新型模/数转换器ADS1282进行数据转换,可获得高保真度、高信噪比、高分辨率的数字信号,同时还可以利用其片上的数据选择器及校准引擎实现自检和系统校准功能,从而保证采集信号质量不随时间、地点、环境和条件而变化。利用ADS1282设计实现的数字化采集单元具有低功耗、小体积、高精度、高分辨率的特点。这里给出ADS1282模/数转换器的特点、工作原理及其在地震数据采集单元中的接口设计。

1 ADS1282简介

1.1 主要特性

ADS1282是一款针对工业应用、具有极高性能的32位、△-∑型模数转换器(ADC)。该转换器具有4阶、固有稳定△-∑调制器,因此具有优良的噪声和线性特性;该调制器的输出既可与片上的数字滤波器联合使用,也可旁路输出到加速处理滤波器;片上多路选择器(MUX)既可提供用于测量的附加的外部输入,也可与内部自检电路相连;片上可编程放大器(PGA)具有极低的噪声和高输入阻抗,易与地震检波器、水听器经一个宽范围的增益连接;数字滤波器可通过编程选择不同的滤波器组合方式;同时片上具有增益及失调检测寄存器支持系统校准功能。ADS12 82的额定工作温度范围为-40~+85℃,最大工作范围可达+125℃,适用于能源探测、地震检测、高精度仪器仪表等要求苛刻的工业应用领域。

ADS1282的主要特性如下:

1)高分辨率:高精度模式,数据输出率为250 SPS时信噪比(RSN)达130 dB,低功耗模式,数据输出率为250 SPS时信噪比(RSN)达127 dB;

2)高精度:总谐波失真(THD)为-122 dB,积分非线性(INL)为O.5 ppm;

3)低噪声可编程放大器(PGA): ;

;

4)2通道多路选择输入(MUX);

5)超量程快速检测功能的4阶、固有稳定△-∑调制器;

6)灵活的数字滤波器:可选择Sinc+FIR+IIR滤波的不同组合方式,其中FIR滤波方式可编程设置为线性或最小相位响应,数据输出率可在250 SPS至4 KSPS之间选择;

7)可设置滤波通带;

8)低功耗:高精度模式为25 mW,低功耗模式为17 mW,待机模式为90μW,掉电模式仅为10μW;

9)失调及增益校准引擎。

1.2 引脚说明

ADS1282采用28引脚TSSOP封装,其引脚配置如图l所示。

CLK:主时钟输入;SCLK:串行时钟输入;DRDY:数据准备好输出,在其下降沿读出数据:DOUT、DIN:串行数据输出、输入;MCLK、M1、M0:若工作在调制器模式,MCLK为调制器时钟输出,M1、MO为调制器的数据输出,否则这些引脚不使用,需接固定值;SYNC:同步输入,用于实现多芯片同步工作;MFLAG:调制器超量程标志,0表示正常,1表示超量程;DGND:数字地,该引脚是接地点的核心;CAPN、CA-PP:PGA输出,在CAPP与CAPN之间需连接一只10 nF的电容;AINP2、AINN2,AINP1、AINN1:正、负模拟输入端;AVDD、AVSS:正、负模拟供电电源,单极性(+5 V)或双极性(±2.5 V);VREFN、VREFP:正、负基准输入;![]() :掉电输入,低电平有效;

:掉电输入,低电平有效;![]() :复位输入,低电平有效;DVDD:数字供电电源:+1.8~+3.3 V;BYPAS:从校准输出:与DGND之间接1μF电容。

:复位输入,低电平有效;DVDD:数字供电电源:+1.8~+3.3 V;BYPAS:从校准输出:与DGND之间接1μF电容。

1.3 内部结构与工作原理

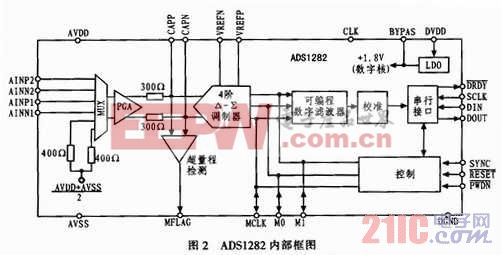

ADS1282的内部结构如图2所示,主要由多路选择器(MUX)、可编程增益放大器(PGA)、△-∑调制器、可编程数字滤波器、增益及失调校准引擎、超量程检测电路、控制器及SPI串行接口等组成。

多路选择器MUX允许5种设置:输入1、输入2、输入1、2之间短路、400 Ω短路测试及共模测试;多路选择器之后是时间连续的差分输入、差分输出CMOS可编程增益放大器(PGA),PGA的增益范围是1~64,可通过寄存器设置。PGA通过300 Ω的内部电阻差分驱动调制器,在CAPP与CAPN之间需接COG型陶瓷电容以滤除调制器采样时产生的瞬时干扰,外部电容用于反混叠滤波,其转折频率可由公式fp=1/6.3x600xC计算。

ADS1282的调制器是一个高性能、固有稳定4阶△-∑调制器,为2加2的通道结构,该调制器在输入过载情况下可进行预测及修复。调制器将待测差分输入信号VIN(其中VIN=(AINP-AINN)PGA)与基准电压VREF(VREF=VREFP-VREFN)相比较,得到1 s密度的数据流,如果输入驱动超过调制器90%但低于100%,调制器仍保持稳定连续的1 s密度数据流,当调制器的输入超出满量程范围时,调制器将进入稳定的饱和状态,这时数字输出代码可能是正满量程值或负满量程值,当输入返回到正常范围时,调制器需要12个调制时钟周期(fMOD)退出饱和状态并返回到线性区域,数字滤波器另外需要62个转换周期才可完全建立数据(线性相位FIR滤波)。

调制器的数据流输出可直接被访问、旁路并禁止输入到内部数字滤波器,也可连接到片上的数字滤波器以提供可读的输出代码。设置CONFIGO寄存器的位FILTR[1:0]=00,可使调制器工作在输出模式,这时引脚MO、M1变为调制器的数据输出,MCLK变为调制器的时钟输出,但不工作在调制器输出模式时,这些引脚为输入引脚且需接固定值。

数字滤波器接收调制器的输出并对数据流进行抽取,通过调节滤波器的数量,可以在精度和数据输出率之间进行折衷,滤波器越多则精度越高,滤波器越少则数据输出率越高。

数字滤波器由3个级联的滤波器组成:1个抽取率可调的、五级sinc滤波器,1个具有可编程相位、32倍率抽取的有限冲击响应(FIR)低通滤波器及1个可编程的、一阶高通滤波器(HPF)。数据可从这3级滤波器模块的任意一级输出,若完全不使用片上滤波器,则可选择滤波器旁路设置(调制器输出),若部分使用片上滤波器,则可选择sinc滤波器输出,表l为滤波器的设置。

- 稳定低噪声放大器中晶体管工作点的设计方法(下)(11-20)

- 24位高精度模数转换器ADSl258的原理应用(11-28)

- 用ADS实现一个2.38GHz全集成化低噪声放大器设计(04-26)

- 基于ADS8364的数据采集系统设计(10-01)

- 发夹型滤波器的设计(10-23)

- 基于ADS1255的地震信息采集模块设计(12-01)