ADS1282及其在单通道地震数据采集单元中的应用

SYNC信号输入将使数字滤波器及调制器执行复位操作,允许多个ADS1282与某个外部事件同步转换。![]() 输入将使寄存器设置复位并重启转换处理,

输入将使寄存器设置复位并重启转换处理,![]() 输入将使芯片进入微功耗状态,注意在

输入将使芯片进入微功耗状态,注意在![]() 模式将不保持原寄存器中的设置,如果希望原寄存器中的设置不变,可使用待机(STANDBY)命令进行设置(在待机模式下静态电流会稍微大一些)。

模式将不保持原寄存器中的设置,如果希望原寄存器中的设置不变,可使用待机(STANDBY)命令进行设置(在待机模式下静态电流会稍微大一些)。

ADS1282根据输入范围选择单电源供电或双电源供电(AVDD和AVSS相互独立),数字电源可为1.8~3.3 V,模拟电源可设置为+5 V以接收单极性信号或设置为较低的±2.5 V内的双电源,以接收真正的双极性输入信号。

2 在地震数据采集单元中的应用

2.1 采集单元的系统构成

该单通道地震数据采集单元设计方案是在分布式地震数据采集系统设计理念的基础上提出的,该数据采集单元可实现单通道地震波信号的原位数字化及数据存储、通信功能,可有效去除模拟信号传输中的干扰信号,提高地震信号采集的质量,地震信号的数据处理、波形显示和记录功能,由控制主机完成。单通道地震数据采集单元的硬件主要由地震信号传感器、模/数转换器、微控制器、存储器、电源管理模块及串行通信接口构成,为达到低功耗、小体积、高精度、高分辨率的设计目的,地震信号传感器选择基于微电子机械系统(MEMS)技术的振动信号传感器ADXL001,微控制器选用高性能、低电压、16位RISC微控制器MSP430F123,此外,为满足大数据量采集的应用需要外扩1个32 KBx8的低功耗FRAM芯片,经模/数转换后的数据首先存入FRAM中,然后通过串行通信接口送到主机,图3为单道地震数据采集单元的硬件组成框图,设计中将模拟电路和数字电路分开供电,触发电路用于实现采集与外部震源同步。

2.2 ADS1282的应用接口电路

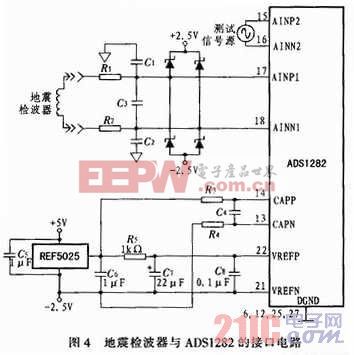

该数据采集单元主要用于陆地勘探,将模拟地震信号传感器(简称地震检波器)拾取的地震波信号转换为数字信号,然后通过串行接口传送到控制主机,为了提高采集信号的质量、有效去除环境造成的噪声干扰,将传感器输出信号通过前端滤波网络送入ADS1282的模拟输入端,接入方式采用差模方式。设计中为提高勘探精度,保证采集信号的质量不会随时间、地点、环境和条件而变化,ADS1282的另一对差分输入端接标准信号源(信号源由专门电路产生),在启动正式数据采集之前可对标准信号进行采集以获得相应的校准参数,然后对ADS1282内部的增益及失调检测寄存器进行正确设置。

图4为地震信号传感器与ADS1282输入前端的应用接口电路,ADS1282采用±2.5 V电源供电。地震信号传感器的输出信号通过R1、R2及C1、C2、C3构成的滤波网络去除高频干扰,为保持良好的共模抑制特性,要求R1、R2匹配精度达到0.1%。电容C3与C1并联可有效降低由于两输入端C1、C2不匹配引起的共模误差,当C3比C1大10倍时,可将因C1、C2不匹配造成的共模误差降低20倍。

ADS1282是高精度模数转换器,要获得最佳性能在PCB设计时应将微控制器、振荡器等噪声较大的数字元件与转换器、模拟前端分开放置,将数字元件放置在靠近电源输入侧以保持尽可能短的数字电流路径,并与敏感的模拟元件分离。箝位二极管用于保护ADS1282的输入信号瞬时超载,当输入信号电平可能超出内部ESD二极管的额定值时该箝位二极管可对输入提供保护。

REF5025为ADS1282提供基准电压,该基准输出通过R5、C7滤波,电容C8为基准输入信号提供高频旁路功能,应将C8放置在靠近ADS1282的引脚端。R3、R4与内部300 Ω电阻形成分压电路为ADS1282提供失调电压,该失调可从通带中除去低电平无用分量,注意该失调与PGA的设置是独立的,该失调电阻同样导致小的附加增益误差。为了保持良好的共模抑制特性,R3、R4匹配精度应达到0.1%,且布线时直接连接到基准输入端。

电容C4用于滤除PGA输出的瞬时干扰信号,该干扰信号是由于调制器采样引起的,该电容同样对输入信号形成一个低通滤波器,具有25 kHz的截频。

3 数据输出接口电路

ADS1282通过串行接口读出转换的数据并访问设置寄存器,ADS1282以二进制补码的格式提供32位转换数据,其中最高位是符号位,‘0’表示是正数,‘1’表示是负数。

ADS1282的串行接口是3线制SPI接口,它包括3个基本信号:SCLK、DIN及DOUT。当转换数据准备好用于回读时,可利用![]() 信号作为判断标志,

信号作为判断标志,![]() 为输出信号,当其变为低电平时表示新的转换数据已准备好。

为输出信号,当其变为低电平时表示新的转换数据已准备好。

数据在SCLK的上升沿移入DIN,而在SCLK的下降沿移出DOUT,若SCLK保持为低电平达64个![]() 周期,则数据传输或命令输入将终止且SPI接口复位,下一个SCLK脉冲将启动一个新的通信周期。当传输中断或SCLK意外失效时可利用这一间歇特性恢复接口,当SCLK无效时需保持低电平。

周期,则数据传输或命令输入将终止且SPI接口复位,下一个SCLK脉冲将启动一个新的通信周期。当传输中断或SCLK意外失效时可利用这一间歇特性恢复接口,当SCLK无效时需保持低电平。

图5为MSP430F123与ADS1282的数据传输及控制接口电路,图中R1~R2取值为47 Ω,为了去除数字信号带来的于扰,在布线时这些电阻应放置在发出信号的一侧,例如信号![]() 是微处理器发出的,R1应放置在靠近MSP430F123的

是微处理器发出的,R1应放置在靠近MSP430F123的![]() 引脚附近,而DOUT信号是由ADS1282发出的,则R4应靠近DOUT引脚放置。

引脚附近,而DOUT信号是由ADS1282发出的,则R4应靠近DOUT引脚放置。

- 稳定低噪声放大器中晶体管工作点的设计方法(下)(11-20)

- 24位高精度模数转换器ADSl258的原理应用(11-28)

- 用ADS实现一个2.38GHz全集成化低噪声放大器设计(04-26)

- 基于ADS8364的数据采集系统设计(10-01)

- 发夹型滤波器的设计(10-23)

- 基于ADS1255的地震信息采集模块设计(12-01)