高性能电源抑制比的线性稳压器

首先,可将LDO稳压器视为一个具有开关功能的低损耗、紧凑型多节低通滤波器。然而,这种模型存在不少局限性,特别是抑制输入端宽带纹波的能力。假设工作电流小于250μA(对于合理的效率而言),IC设计师可以在低静态电流引起的增益带宽极限内优化一些主要性能,如噪声、调节和电源抑制比等。进一步的性能改进需要采取其它一些措施。

当需要高性能电源时,设计师应从向稳压器中增添尽可能多的功能开始。以下将以输出噪声为9μVrms、电源抑制比在10kHz时为80dB的AS1358-9组件为例,说明LDO设计实例。

电源抑制

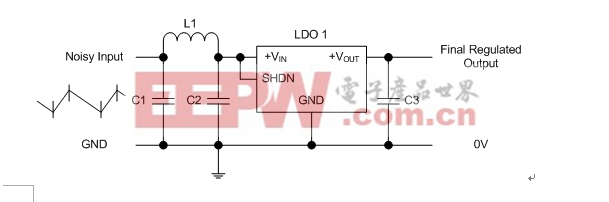

在实际应用中,非理想的组件和寄生电容会改变线性稳压器的理想抑制特性。图1显示了改变或降低电路抑制能力的一些显著缺陷。

图1:P信道LDO显示了简化的寄生高频通道。

线性调节率

LDO数据手册中有两个指标用于描述LDO抑制输入电压噪声等的能力,分别是线性调节率和电源抑制比(PSRR)。虽然它们看起来非常相似,但其中一个指标反映的是直流变化,另一个指针反映的是交流性能。

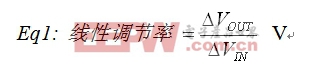

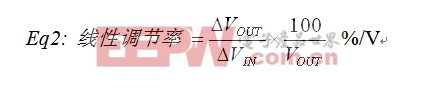

线性调节率代表了LDO抑制输入电压变化的能力。以下式表示:

在实际应用中,线性调节率可被视为稳压器输出电压VOUT随每伏特输入电压Vin变化的百分比,当同样的稳压器具有各种输出电压微调功能时这一点特别有用。

线性调节率是一个稳态直流参数,主要由零频率点上稳压器的开环增益所决定。

电源抑制比

这个指标衡量的是稳压器抑制叠加在正常输入直流电压上的交流信号的能力。

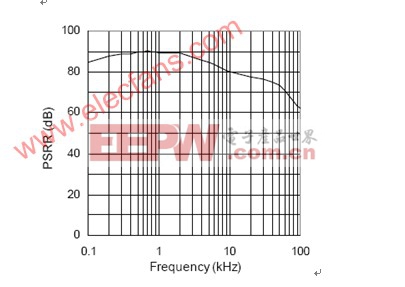

电源抑制比在低频时最大,依照实际稳压器设计,从1kHz到10kHz范围内开始下降。图2为AS1358-9 150mA/300mA低噪声、高电源抑制比LDO的典型PSRR特性。该组件在100kHz时仍具有60dB的良好PSRR值。

图2:AS1358-9组件的电源抑制比。

图2所示的曲线,是由取决于感兴趣频率的众多主导影响共同形成的。在直流与接近100Hz到1kHz区间内,抑制效果取决于带隙基准和稳压器误差信号放大器的开环增益。而在该区间之上直到约100kHz,抑制效果主要取决于误差信号放大器的开环增益。但在100kHz以上时,电源抑制比主要受输出电容、寄生组件以及调整管上的任何漏电流及封装影响。图1标示了这些组件。

如果对100kHz以上频率有额外的电源抑制要求(通常也是需要的),那么在输入端必须连接一个外部的预滤波网络来增强LDO的抑制性能。

外部网络

在实际应用中,只有两种预滤波方法值得考虑,这是因为必须防止在额外的组件上产生过多功耗,同时要保持稳压器的稳定性。

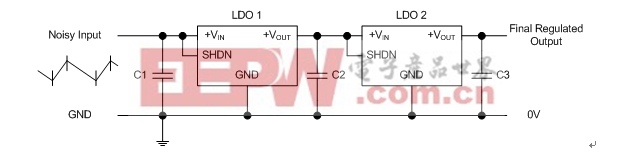

图3:串联LDO可产生很高的PSRR。

图4:外部输入网络可提供额外的抑制性能。

方法1──增加一个线性稳压器。这种方法非常简单,仅需占用少量PCB面积(如AS1358-9要用到2个TSOT23-5封装),与其它方法相较设计时间最短。将两个线性稳压器串联,可使任何频率点的PSRR增加一倍(假设两个稳压器完全相同)。这种方法的缺点是压降会加倍,而且需一个额外的电容。两个AS1359串联后的典型压降在300mA负载电流时为280mV,在100kHz时的抑制比为120dB。要达到这样的水平,必须仔细处理组件的布局和PCB走线。

从实用角度考虑,每个LDO上应允许350mV到400mV的压降。AS1358-9 LDO稳压器的输出电压范围为1.5V到4.5V,调整步进是50mV,因此特殊电压不是问题。

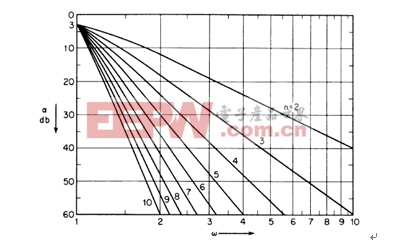

方法2──输入端加载基于统一耗散网络的LC滤波器。三极点巴特沃斯特性需要串联低值线圈和两个电容,其中一个电容通常位于LDO输入端。三极点巴特沃斯响应在4.5Fo处可提供额外40dB的抑制,其中Fo是-3dB点(见图5)。

图5:不同阶数N下的巴特沃斯阻带衰减。

相较方法1,额外的滤波器网络不会增加显著的直流阻抗损耗。不过设计时要特别小心,确保所选电感能够支持要求的直流电流而不至于饱和。巴特沃斯是很有用的特性,其中的通带特别平坦,这点与切比雪夫特性不同,后者为了获得更好的衰减率会牺牲通带和阻带纹波。图7显示级数在2和10之间的巴特沃斯滤波器衰减特性。

图6提出了归一化到1Ω源阻抗和1rad/s频率下的元件值。注意,滤波器输出端并未端接终端电阻,这将允许将其连接到线性稳压器的高输入阻抗上。D栏包含了由

模拟电路 模拟芯片 德州仪器 放大器 ADI 模拟电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)