实现一种数字可调的升压型开关电源的设计方案

1 设计方案

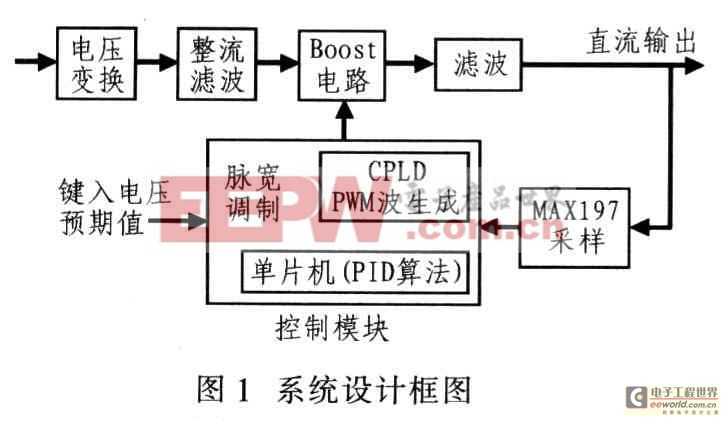

方案系统设计框图如图1所示,输入为220 V,50 Hz交流电压,经电压变换,整流滤波后得到18 V的直流电压,送入Boost电路,经滤波输出直流。CPLD与单片机组成的数字控制模块输出脉宽调制信号(PWM),由按键控制改变PWM占空比,从而控制Boost电路的输出电压。该输出电压可在30~36 V范围内步进调节,实现多路电压输出。最大输出电流高达2 A。

输出电压经MAXl97 A/D采样,送至控制模块,通过PID算法计算调整下一次传送的控制信号,形成反馈回路,实现宽电压输入,稳压输出的功能。

2硬件电路设计

2.1 硬件电路图

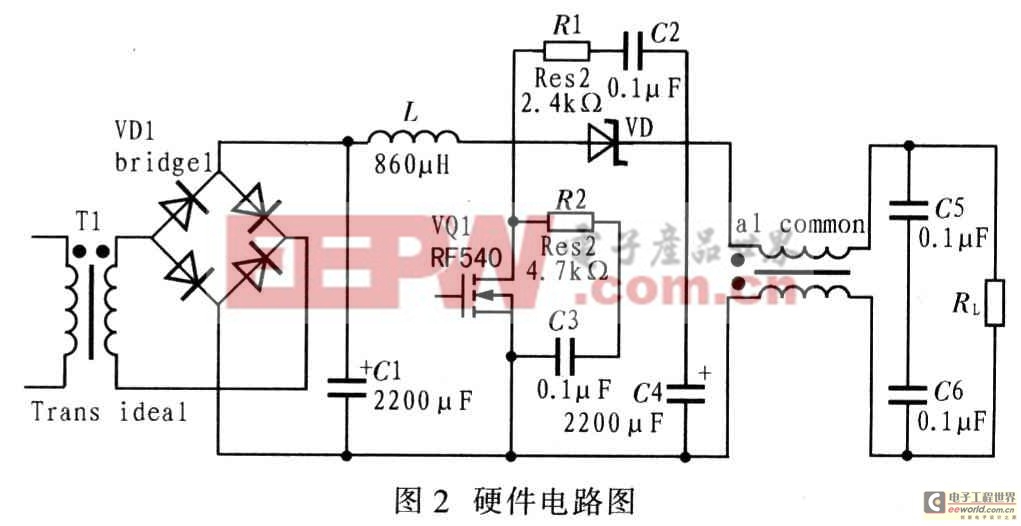

系统硬件电路如图2所示。交流电压经变压器转换,其幅值按一定比例降低。降低的交流电压经扁桥式整流电路整流为18 V直流,经2 200μF电容滤波后进入主转换电路与Boost电路。

在Boost转换电路中,增加MOSFET和二极管缓冲吸收电路,减小过压或过流引起的损耗。由于电源功率较小,则采用RC吸收电路。当过流、过压产生时,电流通过电阻以热能的形式将能量散发出去,降低对MOSFET的影响,减小其损耗,延长使用寿命。根据多次试验,保护吸收电路的电阻应取kΩ级,电容取nF级。直流信号再经低通滤波器滤除纹波,驱动负载。[next]

2.2 主要功能电路原理

硬件电路部分的主要电路是Boost电路,它由功率开关管VT、储能电感L、续流二极管VD和滤波电容C组成。开关管按一定频率工作,转换周期为T,导通时间为Ton,截止时间为Toff,占空比D=Ton/T。其工作原理为:当VT导通时,电感L储能,VD反偏截止,负载由电容C提供电能;VT截止时,L两端电压极性相反,VD正偏,同时为负载和滤波电容C提供能量。

由储能电感L导通和截止期间,电流变化量相等可得,输出电压U0和输入电压U1之间关系为:

U0/Ui=1/(1一D) (1)

2.3 器件选取

根据理论计算,功率开关采用晶体管即可满足要求,故系统采用IRF540型MOS管,其VDS=100 V,IDS=17 A。采用MOS管专用驱动器件IR2110完成驱动功能。IR2110是一款高低电平驱动器件,其逻辑输入电压只需3.3 V,输出电压最大可达20 V,驱动电流最大可达到2 A。其延迟时间为10ns,上升沿和下降沿时间分别为120 ns和94 11s。由于IR2110可同时驱动双MOS管,因而系统只涉及一个MOS管,故只使用一路驱动即可。

由于普通二极管的反向恢复时间过长,而肖特基整流管无电荷储存问题,可改善开关特性。其反向恢复时间缩短到10 11s以内。但其反向耐压值较低,一般不超过100 V。因此肖特基二极管适用于低压、大电流状态下工作,并可利用其低压降提高低压、大电流整流(或续流)电路的效率。

2.4 重要参数的计算

滤波电容的选取,可根据

当开关管工作频率取F=40 kHz时,设纹波电压约为30~50 mV,则计算得到C数量级为1 000μF。实际调试后取电容为2 200μF。[next]

储能电感的选取,可根据:

设计过程中,设置纹波电流△iL=O.4 A,计算得到L数量级为l mH,实际调试后取电感为0.79 mH。[next]

3 软件设计

选择CPLD和51系列单片机组合设定数字控制和输出电压步进。用单片机控制整个系统。软件设计除设定初始电压值,还包含PID算法程序,以及调整PWM占空比。可编程逻辑器件CPLD可直接生成PWM波控制开关管驱动器。

3.1 PWM波产生

PWM波的产生采用Verilog HDL硬件描述语言在CPLD中实现。信号频率设定为40 kHz,采用DDS方式步进频率可精确至1 Hz。使用QuartusⅡ自带的工具生成PLL器件,将外界晶体振荡器输入的频率倍频至100 MHz。由DDS公式,可得:

式中:k为累加系数;Fin为输入频率;n为计数器位数。

当键盘键入所需电压U0,单片机内转化为占空比DY=1一(Ui/U0)。累加器开始累加时输出高电平,当DY达到计数值时变为低电平,最终可得精确频率下占空比可调的PWM控制信号。

3.2 PI控制算法

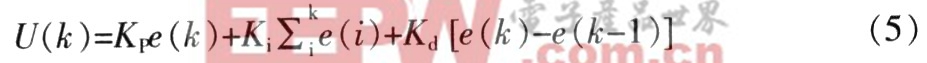

该系统设计选择PI算法(PID算法的一种简单形式),即令Kd为零,只考虑比例系数和积分系数。因此,系统稳压控制的优劣取决于参数Kp、Ki。Kp 越大,系统反应越灵敏,但Kp偏大会导致输出振荡大,调

模拟电源 电源管理 模拟器件 模拟电子 模拟 模拟电路 模拟芯片 德州仪器 放大器 ADI 相关文章:

- 采用数字电源还是模拟电源?(01-17)

- 模拟电源管理与数字电源管理(02-05)

- 数字电源正在超越模拟电源(03-19)

- 数字电源PK模拟电源(04-03)

- TI工程师现身说法:采用数字电源还是模拟电源?(10-10)

- 开关电源与模拟电源的分别(05-08)