两种增强PFC段性能的方法

对于较低功率的应用而言,临界导电模式(CrM)(也称作边界、边界线甚至是瞬态导电模式)通常是首选的控制技术。这种控制技术简单,市场上有采用这种技术的不同的商用控制器,容易设计。然而,高输入电压时,如果输入和输出电压之间的差距小,PFC段会变得不稳定。本文将说明解决这种问题的方法。PFC段一个更加常见的问题是通常发生在启动时的大电流过冲,而不论采用的是何种控制技术。

临界导电模式工作

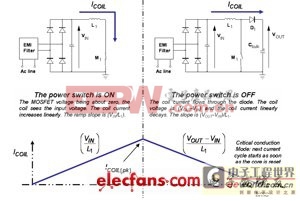

临界导电模式(CrM)工作是低功率应用中最常见的解决方案。这种控制方法可以采用可变频率控制原理来描述特征,即电感电流先上升至所需线路电流的2倍,然后下降至零,接着再上升至正电流,期间没有死区时间(dead-time),如图1所示。这种控制方法需要电路精确地检测电感的磁芯复位。

图1 临界导电模式工作

零电流检测

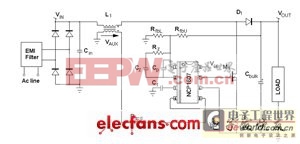

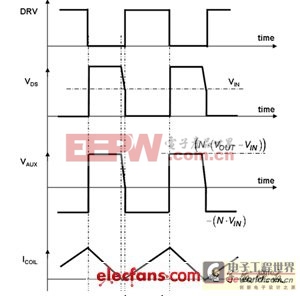

确定退磁完成的常见解决方案在于感测电感电压,更具体地说,就是检测电感电压何时降至零。监测线圈电压并非经济的解决方案。相反,这升压电感与小型绕组相关,这绕组(称作“零电压检测器”或ZCD绕组)提供了电感电压的一个缩小版本,能够用于控制器上,如图2所示。ZCD绕组采用耦合形式,因而它在MOSFET导电时间(反激配置)期间呈现出负电压,如图3中所示。这绕组提供:

VAUX=-NVIN,当MOSFET导通时;

VAUX=N(VOUT-VIN),当MOSFET开路时。

其中,N是辅助绕组与主绕组之间的匝数比。

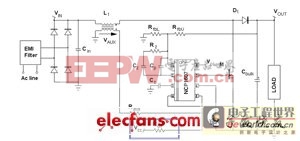

图2 NCP1607驱动的应用段典型应用示意图

当ZCD电压(VAUX)开始下降时线圈电流会达到零。许多CrM控制器内部比较VAUX与接近0V的ZCD参考电压,检测出下降沿,并准时启动下一个驱动信号。为了实现强固的工作,应用了磁滞机制,并实际上产生较高的(upper)阈值(VAUX上升时有效)及较低的(lower)阈值(VAUX下降时有效)。出于不同原因(如安森美半导体NCP1607 PFC控制器中的ZCD引脚的多功能性),在大多数商用器件中这些阈值都相对较高(在1V及2V之间)。

例如,NCP1607数据表中可以发现下述的ZCD阈值规范(引脚5是监测ZCD信号的电路)。

Vpin5上升:最低值为2.1V,典型值为2.3V,最大值为2.5V;

Vpin5下降:最低值为1.5V,典型值为1.6V,最大值为1.8V。

要恰当地检测零电流,VAUX信号必须高于较高的阈值。

图3 波形

极高输入线路时的不精确零电流检测

图4及图5显示出在高线路时会面对的一个问题。VAUX电压在退磁相位期间较小,而这时Vin较高,因为VAUX与输出输入电压差成正比VAUX=N(VOUT-VIN)。此外,如图4所示,输入电压在开关频率呈现出交流含量。因此,VAUX波形并不平坦,相反,它还包含纹波。在低线路时,这纹波可以忽略不计。在高线路时,VAUX幅度在退磁相位期间较小。因此,这些振荡可能大到足以导致过早检测电感磁芯复位。事实上,如图4和图5所示的那样,零电流检测的精度降低了。

图4 不精确零电流检测导致的不稳定性

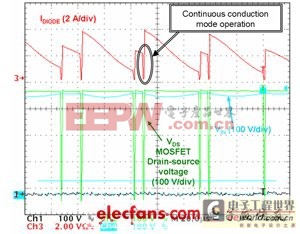

图5 连续导电模式工作

图4显示出现不稳定性问题时高输入线路(正弦波顶端,此处Vin约为380V)下的VAUX电压。我们可以看到MOSFET关闭时,VAUX电压轻微跃升至高于ZCD阈值。由于其大纹波的缘故,在退磁相位期间,VAUX电压首先增加,然后下降。由于在某些开关周期的末段VAUX接近ZCD阈值,这VAUX电压下降导致零电压比较器在电感磁芯完全复位前就翻转(trip)。图5证实了这一论断。有时,升压二极管仍在导电时,PFC段开始新的周期。这个现象主要导致线路电流失真(见红色迹线)、功率因数退化,并可能有一些频率处在耳可听到的噪声。

改善高线路工作的简单调整方法

如图6所示,在VCC与引脚5(ZCD引脚)之间布设一颗电阻,能够减轻或抑制这个现象。这样一来,ZCD引脚上就产生了偏置。

图6 ZCD引脚上的调整

在测试的应用中,VCC为15V,且Rzcd=68kΩ。在VCC与引脚5之间增加一颗电阻Roff=680kΩ,就改变了施加在引脚5(ZCD引脚)上的电压。退磁相位期间ZCD引脚上施加的实际VAUX电压就变为:

(1)

然后,施加在引脚5上的电压就偏置。事实上,这就像是VAUX电压与减小了1.36V的ZCD阈值比较。这样一来,新的实际ZCD阈值就是:

Vpin5上升:最低值为0.74V,典型值为0.94V,最大值为1.14V;

Vpin5下降:最低值为0.14V,典型值为0.24V,最大值为0.44V。

这些降低的ZCD阈值增加了ZCD的精度,并能抑制CCM工作,在相同条件下获得的波特图(见图7)就证实了这一点。

图7 调整改善器件工作

必须注意,Vpin5下降(我们的案例中是1.5V)时,偏置必须保持在低于ZCD最低阈值。这是为了确保新的实际ZCD阈值(Vpin5下降时) 保持高于0V。否则,系统可能难于检测磁芯复位并因此启动新的开关序列。出于这个目的,应当考虑到VCC的变化。

启动时的大过冲

PFC段

- 关注能效性能,提高性能,节约能源(06-24)

- 一般性柔性线路板的性能与参数(06-30)

- 新型放大器实现高性能电流检测(08-18)

- 简化Li+电池充电器CC-CV充电测试(01-16)

- 一种高效反激式开关电源的设计与性能测试(10-05)

- 高性能中频采样系统的设计与实现(02-13)