两种增强PFC段性能的方法

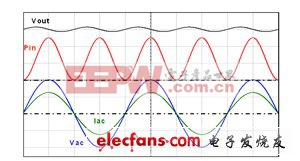

从输入线路正弦波电压源吸收正弦电流,因此,它们为负载提供仅匹配平均需求的方波正弦功率。输出电容(大电容)“吸收”实际提供的功率与负载消耗的功率之差值。

● 馈送给负载的功率低于需求时,输出电容放电,补偿功率差额。

● 提供的功率超过负载功耗时,输出电容充电,存储多余的能量。

因此,输出电压呈现出输入线路频率2倍的低频交流含量。不利的是,PFC电流整形(current-shaping)方法均基于控制信号无纹波的假设。否则,就不能够优化功率因数,因为输入线路电流重新复制了控制信号失真。这就是众所周知的PFC电路动态性能差的原因。它们的稳压环路带宽设得极低,从而抑制100Hz或120Hz纹波,否则输出电压就会注入这纹波。

由于系统极慢,PFC段遭受陡峭的负载或输入电压变化时,会在大电容上呈现出大的过冲(over-shoot)或欠冲(under-shoot)。启动序列就是这些瞬态中的一种,能够产生大的电压过应力(over-stress)。

图8 输出电压纹波

图9展示能在启动相位期间观察到的那类过冲。这波特图是使用由NCP1607驱动、负载是下行转换器的PFC段获得的。

图9 启动相位期间的过冲

承受启动过冲

应用软启动是减小过冲的一种自然选择。然而,设计人员所选择的控制器并不必须具有这个功能特性。此外,从定义来看,这种功能减缓了启动速度,而这并非总是可以接受。

另外一种简单的选择涉及在反馈感测电阻分压器处增加一个电容,如图10所示。在这个图中,我们假定感测网络中上部的电阻分割为两个电阻,而电容Cfb并联连接在其中一个电阻的两端。

10 小幅调整反馈网络

如果控制电路中嵌入了传统的误差放大器,让我们分析电容Cfb的影响。在稳态,Cfb改变了传递函数。通过检测,我们立即注意到它增加了:

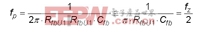

处于下述频率的一个零点:

(2)

处于下述频率的一个极点:

(3)

控制器集成了传导误差放大器(OTA)时,情况就有点不同。这是因为反馈引脚(误差放大器的反相输入)不再是虚接地(virtual ground)。因此,电阻分压器中下部位置的电阻(RfbL)影响了极点频率的表达式。实际上,采用OTA时:

(4)

然而,PFC输出电压的稳压电平通常处于390V范围,而控制器参考电压处在少数几伏的范围。因此,与(RfbU1+RfbU2)相比,RfbL极小;如果RfbU1与RfbU2处在相同范围,或如果RfbU1小于RfbU2,我们就可以考虑:RfbL=RfbU2。事实上,设计人员基于这些考虑因素,能够得出近似Cfb产生的极点频率,即:

(5)

最后,两种配置中都获得相同的极点。

这些条件(RfbU1≈RfbU2)或(RfbU1≤RfbU2)并非限制性条件。相反,满足这些条件是明智之举,因为RfbU1两端的电压及相应的Cfb两端的电压取决于RfbU1值与(RfbU1+RfbU2+RfbL)总电阻值的相对比较关系。这就是为什么它们是现实可行的原因。

如果RfbU1与RfbU2这两个电阻拥有类似阻值,

(6)

如果RfbL=RfbU2:

(7)

最后,如果与RfbU2相比RfbU1极小,我们就获得在控制至输出传递函数中抵消(cancel)的极点和零点。这样,增加Cfb就对环路和交越频率没有影响。如果RfbU1与RfbU2处在相同范围,低频增益就略微增加,交越频率就以跟fp与fz的相同比率增加。事实上,特别是在RfbL=RfbU2时,这个增加的电容并不会大幅改变PFC段的动态性能。

然而,在启动相位期间,这个电容发挥重要作用。当输出电压上升时,Cfb电容也充电。Cfb充电电流增加到反馈电流中,所以稳压电平临时降低。这增加的电流与Cfb电容值成正比,并取决于输出电压的陡峭度,因此,在输出电压快速充电时,这个影响更引人注目。

实际验证

在应用中已经测试了调整方法,反馈网络如下所示:

RfbU1≈RfbU2=470kΩ

RfbL=6.2kΩ

电阻RfbU1两端放置了一个100nF电容。它必须是一种高压电容,因为若我们假定输出电压最大值为450V,它两端的电压可能达到223V。作为一项经验法则(rule of the thumb),我们选择了100nF电容值,这样,在观测到过冲时,时间常数(RfbU1Cfb)就处在启动时间的范围之内。

图11比较没有时的启动序列(左图)与有Cfb时的启动相位(右图)。这些波特图清楚显示电容的影响。Cfb充电电流人为地增加了输出电压(即图中的Vbulk)充电期间的反馈电流,导致预期的控制信号(Vcontrol)放电。因此就没有观测到输出电压过冲。我们可进一步指明,启动时间未受明显影响。

图11 有Cfb(左图)及没有Cfb(右图)时的启动特性

图12显示了没有Cfb时(左图)及有Cfb时(右图)PFC段对突兀的负载改变(120W阶跃)的响应。我们的案例中(RfbU1=RfbU2),Cfb产生并不会相互抵消的额外极点及额外零点,且轻微改变环路特性。然而,最重要的是,采用Cfb还是改善了响应,因为较大的输出偏差(Output dev

- 关注能效性能,提高性能,节约能源(06-24)

- 一般性柔性线路板的性能与参数(06-30)

- 新型放大器实现高性能电流检测(08-18)

- 简化Li+电池充电器CC-CV充电测试(01-16)

- 一种高效反激式开关电源的设计与性能测试(10-05)

- 高性能中频采样系统的设计与实现(02-13)