基于门控时钟的低功耗电路设计方案

集成电路工艺节点的提升带来了芯片集成度的极大提高,同时也导致了功耗的急速增加。另外,市场对电子设备的大量需求使得系统功耗成为系统性能的一个重要指标,功耗的高低成了芯片厂商竞争力的焦点之一,功耗控制与管理已成为绝大多数芯片厂商首要考虑的问题。SoC设计的功耗包含两部分:静态功耗和动态功耗。静态功耗主要由泄漏电流引起,在130 nm工艺下,静态功耗相对较小,可以忽略不计。动态功耗主要包括短路功耗和翻转功耗,是本设计功耗的主要组成部分。短路功耗即内部功耗,指由器件内部由于P管和N管在某一瞬间同时导通引起的瞬时短路引起。翻转功耗由CMOS器件的输出端负载电容充放电引起。芯片工作时,很大一部分功耗是由于时钟网络的翻转消耗的,如果时钟网络较大,这部分引起的功耗损失会很大。在众多低功耗技术中,门控时钟对翻转功耗和内部功耗的抑制作用最强。本文主要讲述门控时钟技术的具体实现。另外,基于高阈值单元具有较低的功耗,设计采用高阈值单元库。

1 门控时钟技术的基本原理

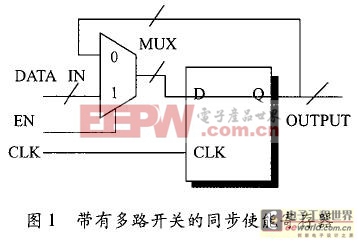

对于一个设计中的寄存器组,经DC编译后一般会生成如图1所示的电路。由图1可以看出,当EN为1时, DATA_ IN的值由多路开关传至寄存器组的数据输入端,当CLK上升沿来临时,传至DATA_OUT。当EN为0时, OUTPUT保持不变。但由于时钟信号CLK的翻转,寄存器组会持续在CLK的上升沿来临时读取数据输入端的数据,而这时读取的数据是不变的,这就消耗了额外的功耗。

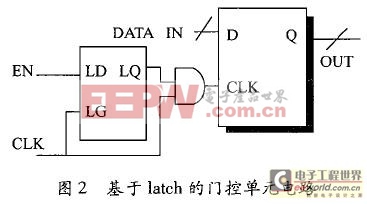

为保证此时寄存器组不受时钟翻转的影响,可在EN信号为0时关断寄存器组的时钟输入端,使其不受CLK端的变化而变化,这一操作可通过门控时钟技术来实现,如图2所示。图中的门控单元由一个Latch和一个与门组成。门控单元也可以采用非latch结构,直接由与门或或门组成。但由于这种电路会引发毛刺,故此处采用基于Latch的门控单元电路。插入门控时钟后,当EN为1时, Latch单元在时钟低电平时将EN锁存至ENL,时钟上升沿来临时, ENCLK随CLK变化,寄存器组执行正常的读入读出操作。当EN为0时,寄存器时钟输入端ENCL保持为0,不随源时钟CLK的翻转而变化,故此时寄存器组不消耗额外功率。

由此可见,插入门控时钟能消除寄存器组冗余翻转引发的内部功耗,同时由于多路选择器组被一个基于latch的门控单元代替,所以也减小了电路的面积。

另外,为了进一步减小设计的功耗,可采用一些特定的门控技术。目前应用比较广泛的有多级门控时钟,层次化门控时钟等。在多级门控时钟技术中,一个门控单元还可用来驱动其他一个或一组门控单元。这样就通过分级控制减少了门控单元的数目,而且这种方法可组合尽可能多的寄存器组使得门控单元向顶层靠近,节省更多功耗。

2 门控时钟的物理实现

电路在功能仿真通过后,开始进行寄存器级综合。采用高阈值标准单元库和多级门控时钟技术相结合,在RTL阶段插入门控时钟单元,并在布局布线时在IC Compiler中进行了基于门控时钟的布局布线优化,布局布线正确完成仿真通过后,在PT中做静态时序分析并进行最终的功耗分析。以下分三个部分讲述。

2. 1 时钟门控的RTL级实现

在RTL级,门控时钟的实现不需要对设计本身进行修改,而只需在综合脚本中加入一些控制项。

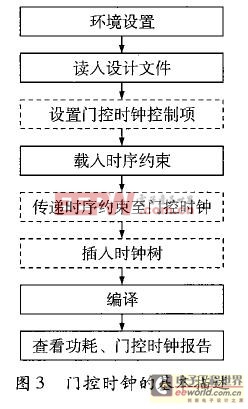

本文采用多级门控时钟,相关的脚本如图3 所示。

图中,传统的综合流程用实线标出。虚线部分为门控时钟的操作。

控制项set_clock_gating_ STyle是门控时钟的核心。它的参数大小决定门控时钟的质量,对功耗的优化效果和对CTS的影响。目前尚无完备的体系介绍如何设置控制项以使门控效果达到最优。本设计中有以下各个参数的设置方法。

首先确定时序单元的类型。为了避免非Latch单元易产生毛刺的缺点,此处选定时序单元的类型为Latch。由于库中提供基于锁存器的门控单元,固正边沿逻辑positive_edge_ logic采用工艺库提供的专用单元。采用集成单元的优势在于不仅不需要设置门控单元输入端建立时间和保持时间,因为集成单元的时序信息在单元库中已有说明,而且有效缓解了插入门控单元对延时带来的不利影响。以下重点阐述实验中bi twIDTh, fanout和stage的确立方法。

fanout的大小对功耗和时序都有影响。数值越大则表示一个门控单元可承受较多的负载,即代表越节省功耗,需要的门控单元也越少,但对门控单元输入端建立时间的要求也就更加严格。位宽决定一组寄存器能被门控的最小宽度。级数则确定多级门控时钟的最大级数。本设计在这三个参数的选取上,主要是依据设计本身对功耗的要求,结合综合时的时序约束和单元库中门控单元的时延信息加以估计,确定一个粗略的

- 基于门控时钟的低功耗时序电路设计(07-13)

- 树电运行低功耗电路在设计中的应用(03-21)

- 树电运行低功耗电路(08-07)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)