异步二进制减法计数器时序分析

时间:02-16

来源:互联网

点击:

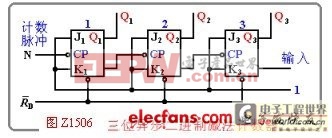

当把图Z1504中的CP端改接到 端,就构成了如图Z1506所示的3位异步二进制减法计数器。令计数器初始状态为000。

第一个计数脉冲来到后,F1处于1状态,同时,输出一个负跳变信号,使得F2也由0态变为1态,同理,F3也处于1态。第二个脉冲来到后,F1由1态变为0态,由0态变为1,但由于是下降沿触发,所以F2仍为"1"态。当然F3的状态也不会变。第三个脉冲来到后,F1由0变为1,由1态变为0,致使F2由1变为0,显然,F3的状态不变。与图Z1504的工作原理类似,低位触发器状态变化两次,高位触发器状态变化一次。这种触发器的时序图和状态表,分别如图Z1507和表Z1502所示。

- 用万用表判定三相异步电动机绕组同名端(06-10)

- PLC控制的防电源短路的电动机正反转控制线路(07-04)

- 一种基于AD9857的信号发生器的设计(09-07)

- 变频器在变频调速时对普通异步电机的影响(08-13)

- 如何设计一个选通脉冲串又不会截短脉冲的电路(04-08)

- N进制异步计数器设计方案(12-06)