DDS的信号模拟器设计

DDS的信号模拟器设计

概述

在雷达的研制和生产过程中,对雷达的性能指标进行调试和检测是雷达研制和生产过程的一个重要环节。如果对雷达性能的测试都采用外场实物的话,即用真实的目标(如舰艇、坦克)给雷达提供测试信号,不仅要耗费大量的人力和物力而且使研制周期变长。因此,目标模拟器一数字模拟技术与雷达技术相结合发展起来的专门的系统,它为雷达的信号处理系统和显示终端技术指标的测试以及性能验证提供必要条件。

1971年,美国学者J.Tierney等人撰写的“A DigitalFrequency Synthesizer”一文首次提出了以全数字技术、从相位概念出发直接合成所需波形的一种新的频率合成原理。如今,DDS技术已成为频率合成技术发展的主流方向,它高度的集成性,对于简化电子系统的设计方案,降低硬件的复杂程度,提高系统的整机性能意义重大。可以预料将来DDS产品的时钟频率将越来越高,杂散会越来越低,价格也将更低,DDS产品将会得到普遍的应用和发展。

1 DDS信号模拟工作分析

1.1 DDS原理

一个频谱纯净的单频信号可表示为:

相应的离散相位序列:

是连续两次采样之间的相位增量。

1.2 总体设计方案

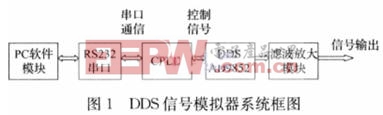

DDS信号模拟器系统主要由DDS信号发生器模块(软件模块、控制器、DDS芯片)、滤波放大模块和调制模块3部分组成。其系统总体框图如图l所示。

1.3 工作流程

首先用户通过运行于计算机上的控制软件,选择要生成的信号,并设置相应的幅度、频率等指标参数,由控制软件将这些要求通过RS232接口传送给CPLD,或利用键盘进行频率选择。CPLD不仅实现根据接收到的控制字对DDS芯片进行设置,并实时地启动DDS芯片使其按要求生成所需要的信号。经过滤波放大,将所生成的信号传送到ASI接口,由此将所生成的基带信号通过雷达(或其他调制器)调制到高频,发射出去。

1.4 软件程序设计方案

上位机软件系统结构如图2所示。

基于DDS的多功能信号模拟器,不仅要能够实现普通射频合成信号源的功能,正如能够在幅度、频率等方面对所需生成的信号加以控制,能够实现定频、扫频以及跳频等输出方式上的选择。同时,该系统增加了叠加噪声模块和灵敏度设置模块,以便能够更好地实现对各种条件下雷达回波信号的模拟。

1.5 DDS射频信号产生电路

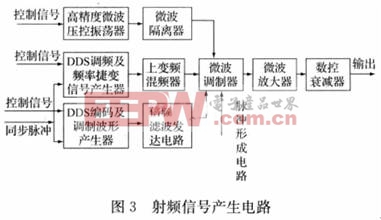

DDS的微波电路构成射频信号产生电路,其组成框图如图3所示,其信号来源分为3路:

第1路是由高精度微波压控振荡器产生频率稳定度很高的微波信号,频率精度:±2.5×10-6,经微波隔离器隔离输出。

第2路是由DDS调频及频率捷变信号产生器产生各种调频(普通调频、线性调频和非线性调频等)和频率捷变信号,DDS工作模式为单音频工作模式时,通过改写频率控制字可实现跳频和频率捷变和频率调制,工作模式为线性调频模式时,通过设定起始频率、频率部进和扫描时间,可实现线性调频。

第3路是由DDS编码及调制波形产生器产生各种编码和调制信号,DDS的一个显著的特点就是在数字处理器的控制下能够精确而快速地处理频率和相位。DDS允许用户对通过改写相位偏移控制字可实现相位的任意控制,码元的产生完全由软件灵活控制,可产生包括二相编码(巴克码、伪随机码)、多相制编码等,并经倍频、滤波和放大后形成调制包络信号。

最后来自第l路微波信号和第2路的变频信号在微波上变频器混频,产生载频信号,来自第3路的调制包络信号和脉冲产生器产生的调制脉冲对载频信号进行调制,形成雷达信号,最后经天线输出。图4、图5为最后输出的波形。

1.6 DDS硬件设计

1.6.1 硬件电路的组成

图6为DDS模拟器硬件电路的组成原理。该信号模拟器主要由6个部分组成:电源电路、串行接口电路、下载电路、FPGA控制电路、AD9852外围电路以及滤波电路。

1.6.2 AD9852外围电路

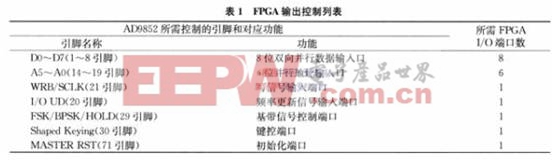

如表1所示,在并行工作模式下,FPGA主要实现对AD9852以下各引脚的控制。

AD9852内部包括1个具有48位相位累加器、1个可编程时钟倍频器、1个反sinc滤波器、2个12位300 MHzDAC、1个高速模拟比较器以及接口逻辑电路。其主要性能特点如下:

(1)高达300 MHz的系统时钟;

(2)能输出一般调制信号,FSK、BPSK、PSK、CHIRP、AM等;

(3)100 MHz时具有80 dB的信噪比;

(4)内部有4*到20*的可编程时钟倍频器;

(5)2个48位频率控制字寄存器,能够实现很高的频率分辨率。

(6)2个14位相位偏置寄存器,提供初始相位设置。

(7)带有100 MHz的8位并行数据传输口或10 MHz的串行数据传输口。

图7为在DDS的信号发生器中AD9852的外围电路设计。

2 测试结果

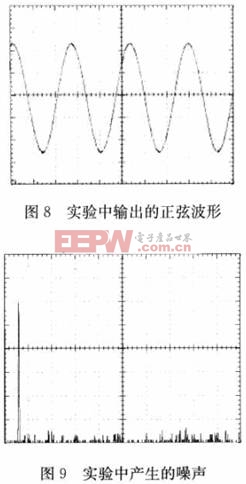

本文设计的DDS信号模拟器输出最大频率受到D/A转换器输出建立时间的限制,因为外接存储器的数据读取时间为15 ns,可编程逻辑器件FPGA的最大时钟频率可达120 MHz。相位累加器的字长为31位,用于寻址波形数据存储器的地址信号为13位;编程产生的正弦波的输出的频率范围是0~120 MHz。其中产生的正弦波如图8所示,但是随着时间的增长,噪声会加大如图9所示。

3 结束语

本文结合DDS信号模拟器的工作原理从理论和实际2个方面,对直接数字频率合成技术(DDS)进行了研究。

首先通过对DDS信号模拟工作理论分析,再通过对DDS射频信号产生电路的研究实验使得微波信号和变频信号在微波变频器上混频,产生载频信号,再者使得调制包络信号和调制脉冲对载频信号进行调制,形成雷达信号,然后经天线输出。最后结合理论分析的结论,通过测试实验得出了系统的性能以及带宽线性调频和带宽10点跳频的过程最终输出了雷达视频 脉冲输出波形,基本实现了设计的要求。

- 一种基于AD9857的信号发生器的设计(09-07)

- 基于FPGA及DDS技术的USM测试电源的设计 (09-08)

- 高性能双通道DDS芯片AD9958及其应用(02-04)

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 基于DDS的调频信号发生器的设计与仿真(04-12)