基于CPLD和VHDL的电梯控制系统设计

随着社会的发展。使用电梯越来越普遍,已从原来只在商业大厦、宾馆过渡到在办公室、居民楼等多种建筑中,并且对电梯功能的要求也不断提高,其相应控制方式也在不断发生变化。电梯的微机化控制主要有:PLC控制、单板机控制、单片机控制、单微机控制、多微机控制和人工智能控制等。随着EDA技术的快速发展,PLD器件已广泛应用于电子设计与控制的各个方面。这里使用CPLD器件,采用VHDL语言设计一个16 楼层单个载客箱的电梯控制系统,此控制系统具有使用安全可靠,功能全面的特点,方便人们生活。

2 系统总体设计

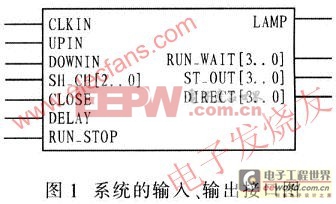

该系统采用单片CPLD器件实现一个多楼层单个载客箱的电梯控制器,该控制器可控制电梯完成 16个楼层的载客服务,而且遵循方向优先的原则,能够提前关电梯门和延迟关电梯门、提供电梯运行的开关控制键同时指示电梯运行情况、楼层间的运行时间以及电梯所在楼层的等待时间。根据系统设计要求,并考虑到系统设计的可验证性,整个系统的输入、输出接口设计如图1所示。

各输入端口的功能如下:

CLKIN:基准时钟信号,为系统提供2 Hz的时钟脉冲,上升沿有效;

UPIN:电梯上升请求键。由用户向电梯控制器发出上升请求。高电平有效;

DOWNIN:电梯下降请求键,由用户向电梯控制器发出下降请求,高电平有效;

ST_CH[2..0]:楼层选择键人键,结合DIRECT完成楼层选择的键入,高电平有效;

CLOSE:提前关门输入键.可实现无等待时间的提前关门操作,高电平有效;

DELAY:延迟关门输入键。可实现有等待时间的延迟关门操作,高电平有效;

RUN STOP:电梯运行或停止开关键。可实现由管理员控制电梯的运行或停止,高电平有效。

以下为输出端口:

LAMP:电梯运行或等待指示键,指示电梯的运行或等待状况。高电平有效;

RUN_WAIT[3…0]:电梯运行或等待时间指示键,指示电梯运行状况或等待时间的长短,高电平有效;

ST_OUT[3…0]:电梯所在楼层指示数码管,指示电梯当前所在的楼层数。即1"16层,高电平有效;

DIRECT[3…0]:楼层选择指示数码管,指示用户所要选择的楼层数,高电平有效。

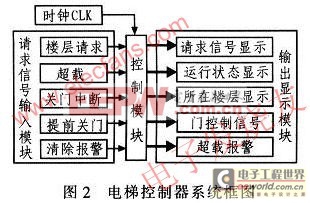

该设计中,电梯的控制状态包括运行状态、停止状态及等待状态,其中运行状态又包含向上和向下状态。主要动作有开、关门,停靠和启动。乘客可通过键入开、关门按钮,呼唤按钮,指定楼层按钮控制电梯。因此,整个电梯控制器应包括5个组成部分:时序输出及楼选计数器;电梯服务请求处理器;电梯升降控制器;上升及下降寄存器和电梯次态生成器,图2为电梯控制器系统框图。图3为电梯控制器的内部组成结构。

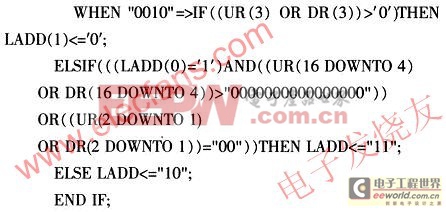

从程序中可以看到,若第3层用户发送上升/下降请求。则电梯处于等待状态;若第3层用户没有发送上升/下降请求,且4~16层的用户发送上升,下降请求,或者1.2层的用户没有发送任何请求,则电梯处于上升状态;反之,电梯处于下降状态。

程序设计中采用方向优先原则,即若电梯处于上升状态,即使有1,2层用户发出上升/下降请求,电梯也不响应,而继续上升,直到响应完所有4~16层用户的请求后,再下降;反之,若电梯处于下降状态,即使4~16用户发出上升/下降请求,电梯也不响应,继续下降,直到响应完所有用户的请求后再上升。

(4)P4进程该进程主要完成电梯运行楼层计数及提前/延迟关门控制。

3 VHDL源程序的仿真

系统程序编写完毕后,在MAX+pluslI软件环境下对其编译仿真。其仿真试验结果如图4所示。

图4中,输入信号为:UPIN,ST_CH,RUN_STOP,DOWNIN,DELAY,CLOSE和CLKIN;输出信号为:ST_OUT, RUN_WAIT,LAMP,DIRECT,DIR,LIFTOR和WAI_T。当时钟上升沿到来时,若WAI_T=0,则它的下一状态为6;因 DELAY信号始终为低电平,故WAI_T依次自减1计数。RUN_WAIT是WAI_T和0的并置运算,故其值和WAI_T相同。

当时钟上升沿到来时,DIR进行加1计数,且当DIR=0XF时,DIR的下一状态值为0。与此同时,DIR加1并赋值给DIRECT。

当LAMP为低电平时,电梯处于等待状态,故LIFTOR保持其原值不变保持0和3不变;当LAMP为高电平时,电梯处于运行状态,因UPIN始终为高电平,DOWNIN始终为低电平,故当RUN_STOP为高电平时,电梯只能处于上升状态,故LIFFOR进行自加1计数,同时,LIFTOR加1赋值给 ST_OUT。

4 硬件实验

在MAx+plusII软件编译完后,采用EPM7128SLC84-6器件下载VHDL源程序,进行硬件试验。

其下载步骤为:首先,指定采用可编程器件EPM7128SLC84-6;其次,依据输入、输出端口指定与之对应的引脚;然后,使用Pof2Jed软件将编译后的下载文件*.Pof。转换成*.Jed文件;最后,使用Atmel ISP软件将转换后的*.Jed文件转换成*.Chn文件。

硬件系统试验

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)

- 基于CPLD的MIDI音乐播放器的设计(06-16)

- 基于CPLD的电器定时开关控制系统设计(08-17)

- 基于CPLD和VS1011E解码器的电梯语音系统设计(11-26)

- 基于DSP和CPLD的软开关电源数字控制器(01-14)

- ADS8323与高速FIFO接口电路的CPLD实现(03-26)