降低热插拔控制电路的电路电流

时间:03-17

来源:互联网

点击:

摘要:当热插拔控制电路的输出发生短路时,会触发内部断路器功能并断开电路。但在内部断路器做出反应之前,刚开始的短路电流可能达到数百安培。通常热插拔控制器断路器的延迟时间是200ns至400ns,再加上栅极下拉电流有限,栅极关闭时间可能需要10μs至50μs。在此期间,会产生较大的短路电流。

本应用笔记给出了一个简单的外部电路,它能将初始电流尖峰降至最小并在200至500ns内隔离短路故障。

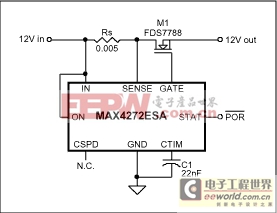

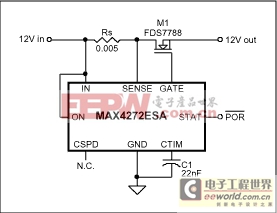

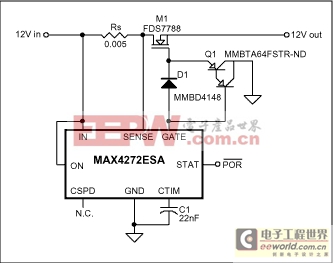

图1. 典型的热插拔控制电路

低速比较器的最低触发门限比正常工作电流高38%,快速比较器的短路触发门限是工作电流的6至8倍。

快速比较器的延迟时间为350ns,这一时段的短路电流尖峰仅受限于电路阻抗。此后电流缓慢下降,直至完全隔离短路故障,3mA栅极下拉电流限制了MOSFET M1栅极电容(3nF至4nF)的放电速率。短路电流在15μs至40μs内缓慢减小,与此同时,栅极电压从19V被拉到接近地电位。

(a) 电源ESR,(b) 短路状态,(c) RSENSE阻值,(d) M1的RDS(ON),(e) M1的ID(ON)。

以上参数均采用最接近实际情况的取值,可以计算出短路时电路的总阻抗:

(电源ESR ≈ 4mΩ) + (短路环节 ≈ 3mΩ) + (RSENSE = 5mΩ) + (RD(ON) ≈ 4mΩ) ≈ 16mΩ。

这时,短暂的峰值电流为:ISC ≈ 750A,并取决于电源的储能电容(带2200μF电容的低ESR背板以750A电流放电时,1μs内电压仅降低340mV)。这种情况下,实际的峰值ISC会由M1的ID(ON)限制到400A左右。

ID(ON)取决于VGS,因此有必要检查电路,以确定这一时段的栅-源电压。MAX4272包含一个内部电荷泵,可使正常工作时的栅极电压高出VIN约7V。因而MOS管导通时VGS = 7V。

短路的第二个影响是它实际上增加了VGS。短路在M1的漏-源之间引入了一个电压阶跃 -等于总输入电压的一部分。由于M1的RD(ON)约为预估的短路总阻抗的1/3,此时施加的VDS约为12V阶跃电压的1/3。由漏-栅电容cdg和栅-源电容cgs组成的分压器会将该阶跃电压的一部分转移到栅极。经过适当计算,可知引入的额外ΔVGS为300mV至500mV,但短路期间进行的测试表明该值可高达ΔVGS = +3V。

至此可以清楚地看出,牢固可靠的短路会在几微秒至几十微秒内产生数百安培的电流。

设计者可能希望将ISC峰值限制在50A,持续时间小于1μs,但如果不增加更快速的比较器和栅极下拉电路的话,这一要求是不切实际的。然而,可以考虑对电路做一些简单的修改。

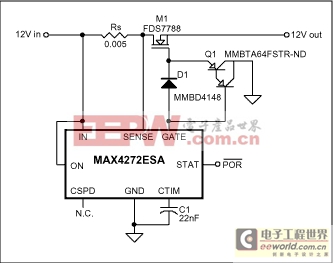

图2. 具有快速栅极下拉的热插拔控制器

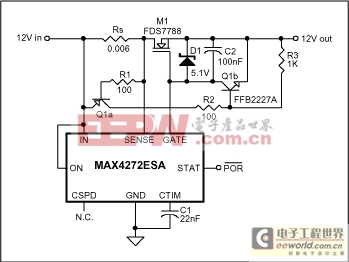

图3. 具有快速短路峰值电流限制功能的热插拔控制器

M1栅极和源极之间的C2可进一步减小发生短路时作用在栅极上的正向瞬态阶跃电压,该电容的取值范围为10nF至100nF。

齐纳二极管D1用来将VGS限制到7V (MAX4272提供该电压)以下的某个值。

虽然齐纳二极管D1在偏置电流为5mA时的额定值为5.1V,但在本电路中,MAX4272仅能输出100μA的栅极充电电流(齐纳二极管偏置电流),因此D1会将VGS限制在3.4V左右。受到限制的VGS可降低ID(ON),当然RD(ON)会增大一些。根据MOS管的数据资料可知:VGS为3.4V时RD(ON)为5mΩ,VGS为7V时RD(ON)为3mΩ。这样可以更快地关断M1。

D1和C2也可以用在图1和图2的电路中,以降低短路时的ID(ON)。

但要产生牢固可靠并且重复性较好的短路情况非常富有挑战性。本测试对以下几种制造短路的方法进行了评估。

本应用笔记给出了一个简单的外部电路,它能将初始电流尖峰降至最小并在200至500ns内隔离短路故障。

典型热插拔电路

我们来考察采用MAX4272构建的+12V、6A典型热插拔控制电路(图1)。根据MAX4272的规格指标,可知其包含触发门限分别为50mV和200mV的低速和快速比较器(整个温度范围内,容限分别为43.5mV至56mV和180mV至220mV)。触发电流大小通常为工作电流的1.5至2.0倍,选择RSENSE = 5mΩ。RSENSE允许有5%的容限,过载条件下低速比较器的触发电流范围是8.28至11.76A;发生短路时,快速比较器的触发电流范围是34A至46.2A。

图1. 典型的热插拔控制电路

低速比较器的最低触发门限比正常工作电流高38%,快速比较器的短路触发门限是工作电流的6至8倍。

快速比较器的延迟时间为350ns,这一时段的短路电流尖峰仅受限于电路阻抗。此后电流缓慢下降,直至完全隔离短路故障,3mA栅极下拉电流限制了MOSFET M1栅极电容(3nF至4nF)的放电速率。短路电流在15μs至40μs内缓慢减小,与此同时,栅极电压从19V被拉到接近地电位。

峰值短路电流

最初350ns内的峰值电流由以下因素决定:(a) 电源ESR,(b) 短路状态,(c) RSENSE阻值,(d) M1的RDS(ON),(e) M1的ID(ON)。

以上参数均采用最接近实际情况的取值,可以计算出短路时电路的总阻抗:

(电源ESR ≈ 4mΩ) + (短路环节 ≈ 3mΩ) + (RSENSE = 5mΩ) + (RD(ON) ≈ 4mΩ) ≈ 16mΩ。

这时,短暂的峰值电流为:ISC ≈ 750A,并取决于电源的储能电容(带2200μF电容的低ESR背板以750A电流放电时,1μs内电压仅降低340mV)。这种情况下,实际的峰值ISC会由M1的ID(ON)限制到400A左右。

ID(ON)取决于VGS,因此有必要检查电路,以确定这一时段的栅-源电压。MAX4272包含一个内部电荷泵,可使正常工作时的栅极电压高出VIN约7V。因而MOS管导通时VGS = 7V。

短路的第二个影响是它实际上增加了VGS。短路在M1的漏-源之间引入了一个电压阶跃 -等于总输入电压的一部分。由于M1的RD(ON)约为预估的短路总阻抗的1/3,此时施加的VDS约为12V阶跃电压的1/3。由漏-栅电容cdg和栅-源电容cgs组成的分压器会将该阶跃电压的一部分转移到栅极。经过适当计算,可知引入的额外ΔVGS为300mV至500mV,但短路期间进行的测试表明该值可高达ΔVGS = +3V。

至此可以清楚地看出,牢固可靠的短路会在几微秒至几十微秒内产生数百安培的电流。

设计者可能希望将ISC峰值限制在50A,持续时间小于1μs,但如果不增加更快速的比较器和栅极下拉电路的话,这一要求是不切实际的。然而,可以考虑对电路做一些简单的修改。

- 在内部快速比较器最初的350ns响应时间内,电流会由ID(ON)限制在几百安以内,此时可以通过增加一个简单的外部电路来加快栅极放电,从而将短路持续时间限制≤ ?μs。

- 或者用一个稍复杂的外部电路将Isc峰值限制在100A范围内,并且持续时间≤ 200ns。

快速栅极下拉电路限制大短路电流的持续时间

只需增加一个PNP型达林顿管Q1,即可极大地缩短大短路电流的持续时间,如图2所示。二极管D1允许栅极在导通状态下正常充电,而关断时控制器的3mA栅极放电电流改为直接驱动Q1的基极。然后Q1在约100ns时间内迅速完成栅极放电。这样,发生短路时的大电流持续时间大为缩短,仅略大于快速比较器350ns的延迟时间。

图2. 具有快速栅极下拉的热插拔控制器

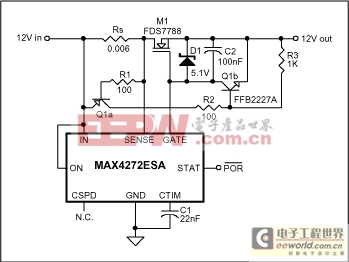

快速限流电路

借助图3所示的电路,可以将短路电流限制在约100A以下,持续时间小于200ns。当RSENSE两端的电压差达到约600mV时,PNP型晶体管Q1a将触发并驱动NPN型晶体管Q1b,从而使M1的栅极电容快速放电。

图3. 具有快速短路峰值电流限制功能的热插拔控制器

M1栅极和源极之间的C2可进一步减小发生短路时作用在栅极上的正向瞬态阶跃电压,该电容的取值范围为10nF至100nF。

齐纳二极管D1用来将VGS限制到7V (MAX4272提供该电压)以下的某个值。

虽然齐纳二极管D1在偏置电流为5mA时的额定值为5.1V,但在本电路中,MAX4272仅能输出100μA的栅极充电电流(齐纳二极管偏置电流),因此D1会将VGS限制在3.4V左右。受到限制的VGS可降低ID(ON),当然RD(ON)会增大一些。根据MOS管的数据资料可知:VGS为3.4V时RD(ON)为5mΩ,VGS为7V时RD(ON)为3mΩ。这样可以更快地关断M1。

D1和C2也可以用在图1和图2的电路中,以降低短路时的ID(ON)。

测试方法-造成短路

没有什么比制造短路更简单了。但要产生牢固可靠并且重复性较好的短路情况非常富有挑战性。本测试对以下几种制造短路的方法进行了评估。

- 不一样的热插拔控制器(04-26)

- 热插拔电路的过热保护方案性能比较(05-12)

- 基于PCI9054和LTC4240的CPCI总线接口设计(05-13)

- 利用PCI1510实现PCI板卡的热插拔测试(05-23)

- 四通道I2C多路复用器提供了地址扩展、总线缓冲和故障管理(06-15)

- 高可靠性电源系统的热插拔原理和应用(11-14)