基于PCI9054和LTC4240的CPCI总线接口设计

CPCI总线简介

CPCI总线是一个开放式、国际性技术标准,由PCI总线工业计算机制造商组织PICMG(PCI Industrial Computer Manufacturer Group)负责制定和支持。CPCI总线具有严格的标准和规范,保证其具有良好的兼容性,支持多种处理器和操作系统,符合CPCI规范的扩展卡可插入任何CPCI系统并可靠地工作。CPCI标准将外设组件互连(PCI)标准特性与支持嵌入式应用的坚固机械外形完美结合在一起,其性能特征是专门针对工业环境而量身定制的。简单的说:CPCI总线=PCI总线的电气规范+标准针孔连接器+欧洲卡规范。CPCI基于ICMG2.0规范,其电气特性与PCI总线相同,因此用户的软件和普通PC机兼容,现有的PCI外围卡也可以很容易地移植到CPCI平台上。CPCI使用高密度针孔总线连接器,和使用金手指连接器的PCI卡相比,具有连接更可靠,完全气密的特点,模块的抗震性和抗腐蚀性高。CPCI还支持热插拔,即可在不关机状态下插入或取出板卡。热插拔的优点在于能增强系统性能或诊断系统故障而无需关闭系统,这对很多应用来说十分重要。

另外,CPCI在32位/33MHz系统中能够提供132MB/s的背板传输能力,在64位/66MHz系统配置情况下的性能为528 MB/s。在对带宽要求高的场合CPCI具有很强的优势。

除了上述所有的优点,CPCI还具有非技术性的优势,即经济实用、可快速推向市场以及高可靠性。所以,在当今的工控、通信、军事等诸多要求高可靠性领域中CPCI总线已经取代了ISA、STD等其它总线,成为主流总线形式。

C PCI系统硬件方案概述

CPCI系统由机箱、电源、总线背板和功能单元组成。一般而言,CPCI机箱内部就带有电源和总线背板,其中CPCI总线背板如图1所示。

CPCI系统最多能加载的CPCI功能单元数取决于机箱所能提供的槽数n:一个CPCI系统由1个系统槽和(n-1)个外围槽组成。在CPCI系统中,系统槽为系统提供仲裁、时钟、中断和复位功能,这些信号对总线上所有的功能单元起作用。

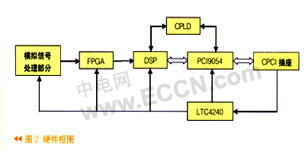

在这个CPCI系统中,我们研制的实际上是一块功能单元板,其硬件框图如图2所示。

由于数字信号处理部分计算量大,且实时要求高,我们采用了FPGA和DSP协同处理数据的方案。在数字信号处理时,低层的信号预处理算法处理的数据量大,对处理的速度要求高,但运算结构相对简单,因而适于用FPGA进行硬件实现,相比之下,高层处理算法所处理的数据量相对较小,但算法的控制结构复杂,适于用运算速度高、寻址方式灵活、通信机制强大的DSP芯片来实现。

CPCI总线控制以及通信协议十分复杂,一般需要选用专门的处理芯片。我们这里选用了PLX公司的PCI9054芯片,而电源管理选用了凌力尔特公司的LTC4240芯片。

CPCI总线接口设计

PCI总线接口的实现

设计PCI接口的实现通常有两种方法:一种是用可编程器件FPGA或CPLD,另一种是用专用PCI接口芯片。二者各有优缺点:利用可编程器件自行设计PCI接口逻辑,可以根据具体的应用需要,优化接口逻辑,灵活性是该方法最大的特点,且接口逻辑也可获得较高的性能。但是由于PCI协议比较复杂,在具体的实现中也相当困难,并且各种逻辑关系验证起来也很麻烦,有时会得不偿失,把简单的设计变得复杂化了;而利用专用芯片来实现PCI总线接口是一种能够解决设计难点的有效方法。但是这种芯片必须具有较低的成本和通用性,而不限于插卡一侧的特定处理器总线,能够优化数据传输,提供配置空间,具备片内FIFO功能(用于突发性传输)等。目前,很多半导体器件公司提供这类专用芯片。如PLX开发的PCI9030、PCI9054 和AMCC开发的接口芯片S5933等。

比较以上两种实现PCI接口的方案可知,用可编程逻辑器件能够较灵活地实现所需要的功能,但为了达到PCI指标的苛刻要求,需要做大量的逻辑验证和时序分析工作。采用PCI专用芯片,可以比较容易地实现PCI接口,大大缩短开发时间,当然,由于厂家设计芯片时对通用性的考虑,在用户需要的某个方面可能不是最好的,但综合性能方面,采用专用芯片要比用可编程器件设计好得多。

我们最终选用了PLX公司的PCI9054芯片。

PCI9054是PLX公司生产的PCI总线通用接口芯片,采用先进的PLX数据管道结构技术,符合PCIV2.1和V2.2规范。提供了两个独立的可编程DMA控制器。每个通道均支持块和分散/集中的DMA方式:在PCI总线端支持32位/33MHz;本地端(local bus)可以编程实现8、16、32位的数据宽度,传输速率最高可达132MB/s。

PCI9054与DSP的接口

PCI9054作为一种桥接芯片在PCI总线和LOCAL总线之间提供传递消息,既可以作为两个总线的主控设备去控制总线,也可以作为两个总线的目标设备去响应总线。其本地总线可工作在M,C,J三种模式:M模式是专为Motorola公司的MCU设计的工作模式。C模式下9054芯片通过片内逻辑控制将PCI的地址线和数据线分开,很方便地为本地工作时序提供各种工作方式,一般较广泛应用于系统设计中。J模式是一种没有Local Master的工作模式。它的好处是地址数据线没有分开,严格仿效PCI总线的时序。

由于DSP我们采用了TI公司的C6202,考虑到与DSP的扩展总线进行接口,PCI9054的LOCAL总线选用了J模式。其连接如图3所示。

- 不一样的热插拔控制器(04-26)

- 热插拔电路的过热保护方案性能比较(05-12)

- 利用PCI1510实现PCI板卡的热插拔测试(05-23)

- 四通道I2C多路复用器提供了地址扩展、总线缓冲和故障管理(06-15)

- 高可靠性电源系统的热插拔原理和应用(11-14)

- 高可靠性电源系统的热插拔原理和应用问答选编(11-14)