一种用于13 bit 40 MS/s流水线ADC中的采样保持电路

近年来,随着通信和多媒体市场的快速增长,数字系统无论在处理能力还是处理速度上都取得了飞速的发展,因此对作为模拟信号通向数字信号桥梁的模数转换器(ADC)的性能要求也越来越高 [1]。在各种ADC结构中,流水线ADC在速度和精度上能够达到合理的折衷,因此得到了广泛应用。在流水线结构ADC中,其前端采样保持电路是整个系统的关键模块之一,其性能直接决定了整个ADC的性能[2]。

本文对流水线ADC的采样保持电路的结构以及主要模块如增益提高型运算放大器电路、共模反馈电路和开关电路进行了分析,并对各个模块进行了设计,最终设计出一个适合于13 bit 40 MHz流水线ADC的采样保持电路,仿真结果表明,该采样保持电路满足设计要求。

1 采样保持电路结构

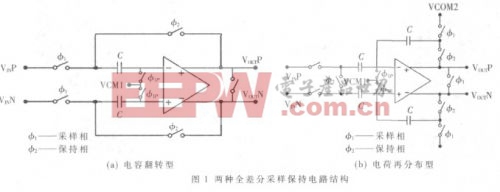

采样保持电路的结构直接决定了采样保持电路的精度和速度,图1为常用的两种全差分结构:电荷再分布型和电容翻转型。全差分结构能够很好地消除直流偏置和偶次谐波失真,并抑制来自衬底的共模噪声。

与电荷再分布型结构相比较,电容翻转型结构的反馈系数为1,是电荷转移型(在Cs=Cf=C时,反馈系数为0.5)的两倍,因此在同样的闭环带宽时,电容翻转式结构所要求的运放单位增益带宽(GBW)只是电容电荷再分布式GBW的一半,所以电容翻转型结构具有功耗小的优点[3]。另外由于电荷再分布型电路需要使用4个电容,但电容翻转型只需要2个电容,在CMOS工艺中,电容需要大的实现面积,电容翻转型结构具有小的实现面积。因此,电容翻转型更适合高速高精度的流水线ADC应用,本文的采样保持电路采用电容翻转式结构来实现。

2 增益提高型放大器的设计

运算放大器是整个采样保持电路中最重要的模块,它的增益和带宽直接决定了采样保持电路的精度和速度。但增益和带宽是相互矛盾的,高增益要求使用多级放大器、小的偏置电流、长沟道器件;而大带宽则要求使用单级放大器、大的偏置电流、短沟道器件,所以放大器是采样保持电路设计的一个难点。

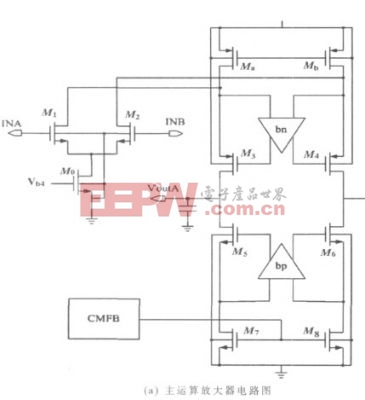

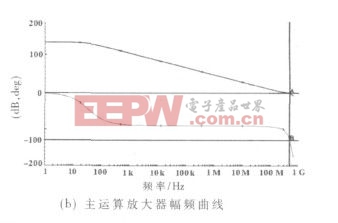

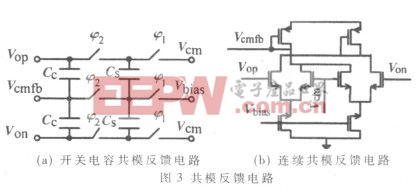

本文主运算放大器采用全差分的折叠式共源共栅结构,并用增益提高技术来提高放大器的增益,达到了高增益和大带宽的要求[4-5]。主运算放大器电路如图2 所示,由于NMOS管的迁移率高于PMOS管,在跨导相同的情况下,NMOS管具有较小的面积,从而使得运算放大器具有较小的输入电容,有利于提高采样保持电路的反馈系数,所以本文采用了NMOS管作为输入对管的折叠式共源共栅结构。两个辅助运算放大器BN和BP分别为NMOS和PMOS管作为输入对管的折叠式共源共栅放大器。图2 中的CMFB模块为主运算放大器的共模反馈电路,由于主运放的输出摆幅较大,所以采用如图3(a)所示的开关电容共模反馈电路,开关电容共模反馈不会受输出摆幅产生限制,并且其只有静态功耗。对于两个辅助运放而言,由于其输出和输入范围很小,所以采用如图3(b)所示的连续时间共模反馈电路,这种电路没有电容,节省了面积。图2(b)为主运算放大器在负载电容为6 pF时的频率特性曲线,其增益为133 dB,带宽约为478 MHz,相位余度为59.7度。整个放大器(包括偏置电路、辅助运放、共模反馈电路)消耗的平均电流为8.5 mA。

3 采样开关的设计

采样开关的性能在采样保持电路中占有十分重要的地位,对于一个简单的NMOS开关,开关导通时其导通电阻Ron为:

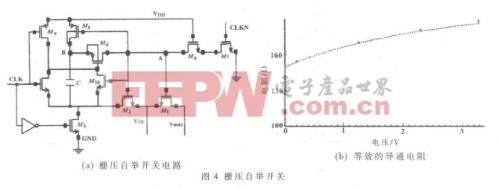

可见,导通Ron是一个与输入信号Vin相关的非线性电阻,这将在输出信号中引入谐波失真 [5]。本文采用如图4(a)所示的栅压自举开关,开关的导通电阻随输入信号幅值变化的曲线图如图4(b)所示,曲线的斜率大约为11 Ω/V,其导通电阻随输入信号幅值的变化较小,具有较高的线性度。

4 仿真结果

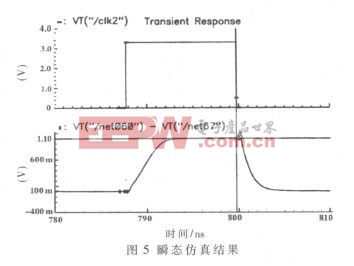

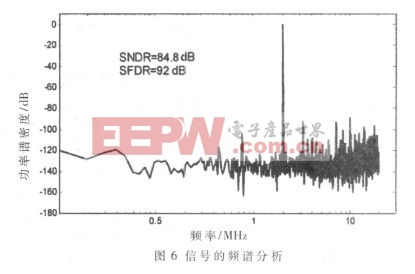

采用TSMC的0.18 μm工艺对电路进行了设计,电源电压为3.3 V,采样时钟为40 MHz,采用Spectre对电路进行了仿真。在采样保持电路的输入端加一值为1 V的阶跃信号,其瞬态仿真结果如图5所示。从图中分析得出,在保持相结束时刻,采样保持电路的输出幅值为1.000 08 V,与理想电压的误差为0.08 mV,建立精度达到了0.008%。图6所示为信号的频谱分析,输入峰-峰值为2 V,频率为1.992 187 5 MHz的正弦信号。对输出信号进行4 096点的FFT, 结果显示, 其SNDR为84.8 dB,SFDR为92 dB,有效位数为13.8 bit,能够胜任13 bit 40 MHz流水线型ADC对前端采样保持结构的要求。整个采样保持电路消耗的平均电流为8.501 mA。

本文设计了一个高速高精度的采样保持电路,可作为13 bit 40 MHz流水线型ADC的前端模块。该采样保持电路为电容翻转结构,采用栅压自举开关提高了开关的线性度,其运算为增益提高型的折叠式共源共栅结构,达到了高速高增益

- 适用于12 bit流水线ADC采样保持电路的设计(01-17)

- 13bit 40MS/s流水线ADC中的采样保持电路设计(09-26)

- bit和byte的关系及区别(01-28)

- 8 bit 800 Msps高速采样保持电路的设计(04-17)

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)