基于PCI总线的大容量雷达数据采集系统的设计

5 利用双缓冲技术实现大容量数据采集

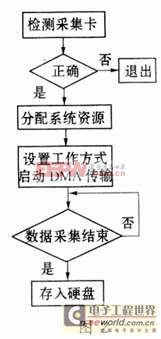

在DOS操作系统下,如果不用扩展内存管理软件,可以分配的系统内存要小于640KB。在Windows操作系统下,可以分配的系统内存虽然要比在DOS操作系统下分配的大,但要分配几十兆甚至几百兆的连续的内存空间是很困难的,所以采用双缓冲技术来实现大容量雷达数据的采集。

在计算机中申请一段连续的内存作为DMA操作的数据缓冲区,其在逻辑上是一个环行缓冲区,它被分成相等的两个部分。另外,根据要采集数据的多少,申请若干个采集缓冲区,其容量为环行缓冲区容量的一半,所申请采集缓冲区的总容量要大于或等于要采集数据的容量。当数据采集启动后,数据先写入环行缓冲区的第一部分(如图3a所示)。当数据写满环行缓冲区的第一部分后开始写环行缓冲区的第二部分时,我们将环行缓冲区的第一部分中的数据移到第一个采集缓冲区,这样就可以腾空环行缓冲区第一部分的空间给以后的DMA数据传输(如图3b所示)。当环行缓冲区的第二部分写满,采集数据将重新往腾空的环行缓冲区第一部分写,这时我们可以将环行缓冲区的第二部分的数据移到第二个采集缓冲区(如图3c所示),这样就可以腾空环行缓冲区第二个部分的空间给以后的DMA数据传输。当环行缓冲区的第一部分写满后,采集数据将重新往腾空的环行缓冲区第一部分写,同时将写满的环行缓冲区的第一部分中的数据移到第三个采集缓冲区(如图3d所示)。以后的采集过程重复前面的工作,如此循环直到数据采集传输结束。当数据采集完成后,将内存中所有采集缓冲区的数据按照采集顺序存入硬盘。

6 结束语

本设计利用了PCI总线突出的数据传输性能,加上采用双缓冲技术,有效地解决了高速大容量数据采集的问题,成功地实现了一百多兆字节雷达数据连续高速采集。PCI总线控制芯片的出现则大大缩短了PCI总线硬件设备的开发周期,同时也使得硬件设备的可靠性和稳定性都有了较大的提高。

参考文献

2 张长隆等.PCI总线接口技术及其在雷达数据采集通道中的应用.微处理机,2000(1)

模拟电路 模拟芯片 德州仪器 放大器 ADI 模拟电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)