基于PCI总线的大容量雷达数据采集系统的设计

关键词:PCI总线,数据采集,VHDL,CPLD

1 引 言

数据采集技术是信号处理一个非常重要的环节,广泛应用于雷达、通信、遥测遥感等领域。在研制基于新型连续波噪声雷达体制的新型连续波雷达时,为了研究更加有效灵活的雷达信号处理算法,利用计算机这个通用的计算和控制平台,先将雷达信号采集到计算机上,然后在计算机上进行雷达信号处理算法的研究。课题要求对雷达I和Q两个通道的信号进行采集,采样精度为12位,最高的采样频率为20兆。传统的基于ISA、EISA和VL总线的数据采集,受到总线带宽、控制方式和实现难易程度的制约,不能满足课题要求。而PCI总线以其峰值传输速率高达每秒132兆字节、支持突发传输等突出的性能,成为我们雷达数据采集首选的计算机IO接口。本文介绍了采用PLX9054作为PCI总线接口芯片的大容量雷达数据采集系统的开发,系统包括数据采集卡和配套软件。

2 数据采集卡系统结构的介绍

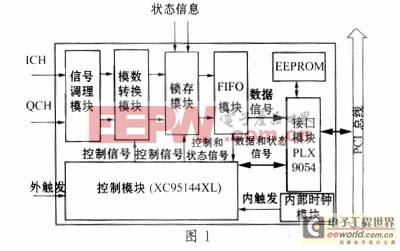

数据采集卡的系统结构如图1所示。雷达输出的I和Q两通道视频信号通过数据采集卡的信号调理模块,经隔离限幅放大后,送到模数转换模块,在这里,两路模拟信号分别被转换成12位的数字信号。两路12位的数字信号经锁存后,被送到FIFO模块缓存起来,这些缓存的数据将通过PCI总线接口模块以DMA方式存入计算机内存。当数据采集完成后,这些内存中的数据将存入硬盘,生成雷达数据文件。每个通道的雷达信号只用了16位中的12位,还有4位未用,我们利用这4位来传输雷达随机二相码码字等一些数字状态信息,这些信息将从锁存模块输入,随雷达信号同步采集到计算机中。

数据采集卡的控制是由控制模块来完成的。内部时钟模块提供内触发信号,它和外触发信号一起接到控制模块,由控制模块根据用户要求来选择使用不同的触发信号。EEPROM内存储有PCI总线接口芯片PLX9054的配置信息。

3.1 接口模块

接口模块的功能是由PLX9054来实现的。PLX9054是PLX公司的一种功能强、使用灵活、并符合PCIV2.2规范的32位33MHz PCI总线接口控制器,它可以作为PCI总线的主控设备去控制总线,也可以作为目标设备去响应总线。PLX9054提供了PCI总线、EEPROM、LOCAL总线三个接口。LOCAL总线有三种工作模式:M模式、C模式和J模式,在实际的数据采集时,将LOCAL总线设置为C模式。选用Fairchild Semiconductor公司的串行EEPROM-NM93CS56L作为PLX9054的配置芯片,该芯片通过EEPROM接口和PLX9054相连。PLX9054的长配置方式要求68个字节的信息,主要包括:设备识别号、供应商代码号、Local总线三个空间的大小以及三个空间的基址等,可以利用编程器事先将要配置的信息写入配置芯片中。在计算机启动时,系统将根据配置信息分配我们申请的系统资源。PLX9054作为一种“桥”芯片,在PCI总线和LOCAL总线之间有三种直接的数据传输模式:

(1)PCIInitiator数据传输模式:LOCAL总线主设备通过PLX9054访问PCI总线存储空间和I/O空间。

(2)PCITarget数据传输模式:PCI总线主设备通过PLX9054访问LOCAL总线存储空间和I/O空间。

(3)DMA数据传输模式:PLX9054作为两总线的主设备,从PCI总线存储空间读数据到LOCAL总线存储空间或者从 LOCAL总线存储空间读数据到PCI总线存储空间。

在实际的数据采集中,我们仅用到PCITarget和DMA两种数据传输模式,PCITarget用于对控制模块中的寄存器进行读写,用于采集方式的设定,DMA用于雷达数据的采集。

3.2 信号调理模块和模数转换模块

采用AD843构成的信号调理模块,对输入的雷达信号进行隔离限幅放大。经过调理后的雷达信号送到高速模数转换芯片AD9042AD的模拟输入端进行模数转换,模数转换时钟由控制模块产生。AD9042AD的模拟电源由DC-DC馈电,DC-DC输出电压的在线稳定度为1.25%,满足AD9042AD模拟电压稳定度5%的要求。AD9042AD是一种高速、高性能、低功耗的12位高速模数转换芯片;它采用两级转换模式,并以与CMOS兼容的模式输出二进制补码,+5V供电,内部提供采样/保持电路以及参考电压;它的转换速率高达41MSPS。

3.3 FIFO模块

利用DMA方式进行数据传输时,接口芯片PLX9054内部用于数据缓冲的FIFO只有32 DWord大小,远不能满足高速连续大容量雷达数据采集的要求。所以,采用在LOCAL总线上外加FIFO的方法来增加用于数据缓冲FIFO的容量,我们采用的FIFO芯片IDT7206L12为16K×9位,所以每路要用两片IDT7206L12来构成16K×18位(只用了16位),两路共要用四片IDT7206 L12。

3.4 控制模块

Xilinx公司的CPLD器件XC95144XL采用了最先进的FastFlash技术,有144个宏单元,3200个门电路,并且具有在系统可编程(ISP)和信号延迟可预测特性,使得它很适合构成较复杂控制器件。在数据采集卡的开发中,采用XC95144XL作为控制模块。控制模块主要协调各个模块的工作,完成数据采集功能。控制模块除了实现数据采集的控制逻辑外,还在其中实现了分频、触发源选择、命令等一些控制和状态寄存器,通过对上述寄存器的读或写,进行数据采集工作方式设定。

由于PLX9054的LOCAL总线工作在C模式,所以XC95144XL经编程后的工作时序要满足C模式的要求。我们采用VHDL逻辑输入方式,利用Xilinx公司的配套软件Foundation Series 2.1对XC95144XL芯片进行编程。由于控制逻辑比较复杂,在编写控制模块的VHDL程序时,采用了分层设计的设计方法。

4 配套软件的实现

雷达数据的采集由数据采集卡在控制模块的控制下自动进行,这就为数据存储提供了有利条件,使主机在对PCI总线控制器和控制模块中的控制寄存器进行必要的初始化后,只进行数据存储工作,提高了数据实时采集与实时存储的速度。在数据采集软件的实现中,采用了DMA工作方式。具体工作过程为:当系统启动后,首先对采集卡进行检测,如采集卡存在则申请并分配系统资源,如内存、中断和DMA资源等,接着,对数据采集卡进行工作方式的设置,并且,启动DMA进行数据传输。在该程序中,以中断方式进行工作,即DMA先将采集的数据传输至主机内存中,当传输达到预定量时,采集结束,调用中断处理程序,将内存中的数据存储到硬盘中,生成雷达数据文件。数据采集软件流程如图2所示。

模拟电路 模拟芯片 德州仪器 放大器 ADI 模拟电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)