为不同接收机前端设计带通滤波器的谐振匹配方法

电路功能与优势

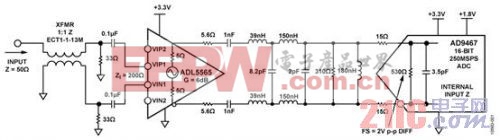

图1所示的电路是一款16位、250 MSPS、窄带、高中频接收机前端,其中在 ADL5565 差分放大器与AD9467 ADC之间提供最佳接口。

AD9467是一款缓冲输入16位、200 MSPS或250 MSPS ADC,具有约75.5 dBFS的SNR性能和介于95 dBFS与98 dBFS之间的SFDR性能。由于具有高输入带宽、低失真和高输出线性度,ADL5565差分放大器适合驱动中频采样ADC。

本电路笔记介绍了如何设计接口电路和抗混叠滤波器才能在保持高性能的同时确保最低信号损耗的系统化过程。使用谐振匹配方法来设计最平坦的巴特沃兹四阶带通滤波器,中心频率为200 MHz。

图1. 使用ADL5565差分放大器和AD9467 ADC完成窄带高中频应用的谐振滤波器设计

电路描述

使用差分放大器来驱动高速ADC的优势包括信号增益、隔离和ADC与源阻抗匹配。ADL5565允许6 dB、12 dB或15.5 dB的引脚绑定增益调整。或者,通过对输入应用两个外部电阻,可在0 dB至15.5 dB范围内实现更精细的增益步进。此外,ADL5565具有高输出线性度、低失真、低噪声和宽输入带宽。3 dB带宽为6 GHz,0.1 dB平坦度为1 GHz。ADL5565能实现大于50 dB的输出三阶交调截点(OIP3)。

为实现ADL5565和AD9467必须提供的最佳性能水平,必须严格遵循各数据手册中指定的设计原则。部分设计准则包括正确匹配ADL5565的输入和输出阻抗以实现最低信号损耗和最佳线性度、抗混叠滤波器使用系统性设计以改善动态范围,以及源阻抗应匹配ADC输入等等。

ADL5565输入阻抗匹配

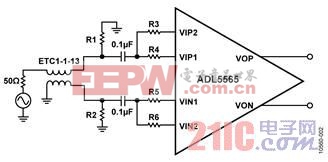

图2. ADL5565输入阻抗匹配

图2显示了建议ADL5565使用的输入匹配网络。ADL5565的输入阻抗与增益相关,6 dB增益下的差分输入阻抗为200 Ω,12 dB增益下为100 Ω,15.5 dB增益下为67 Ω。为使信号发生器的50 Ω源阻抗与ADL5565的输入阻抗匹配,R1和R2必须加以选择,使两者之和与ADL5565的输入阻抗ZI并联后等于50 Ω。为维持差分电路内的平衡,R1必须等于R2。以下公式可用于计算必要的匹配电阻。

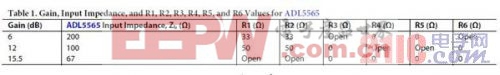

表1显示了计算后的端接电阻和用于ADL5565的不同增益设置的引脚配置。

图2所示配置的替代方案是以阻抗转换RF变压器取代1:1巴伦ETC1-1-13。这样可以无需使用R1和R2。6 dB增益配置可使用1:4变压器,12 dB增益配置可使用1:2变压器。此替代配置的优点是元件数更少,信号损耗更低。不过应注意变压器的带宽。与1:1巴伦相比,阻抗转换变压器的带宽更窄,插入损耗更高。

图2显示了使用巴伦或变压器驱动ADL5565的单端转差分方法。此配置在某些应用中可能不可行或无必要。ADL5565的驱动器接口具有灵活性,例如可以单端(图示)或使用差分混频器以差分方式来驱动。有关不同输入接口的详情请参考ADL5565数据手册.pdf。

ADL5565输出负载匹配

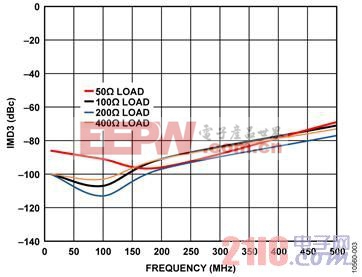

ADL5565线性度性能已针对200 Ω输出负载进行了优化。这是常见的输出阻抗,用于与ADC接口和滤波器设计。在200 Ω的优化输出负载下,ADL5565在200 MHz时的输出IP3为46 dBm。

如果200 Ω输出负载不适合应用,可在ADL5565的输出负载与线性度性能之间权衡。图3显示了三阶交调(IMD3)与常用输出负载频率的曲线图。

图3. ADL5565 IMD3与用于50 Ω、100 Ω、200 Ω和400 Ω输出负载的频率的关系,3.3 V电源,增益 = 6 DB

AD9467源阻抗

AD9467在此电路中是ADC的理想之选,因为它是针对宽带宽范围内的高性能以及易用性进行优化的中频采样ADC。AD9467具有集成式缓冲器,用以对驱动器放大器提供固定输入阻抗。此输入结构优于使用直接耦合至采样开关的无缓冲前端的ADC。无缓冲ADC对驱动放大器提供随时间变化的输入采样保持阻抗。加入输入缓冲器可放宽驱动要求,但代价是功耗略高。AD9467的缓冲式源阻抗被建模为530 Ω电阻的固定阻抗,与3.5 pF电容并联。

与ADC接口时,建议从530 Ω减去真实输入阻抗,到达200 Ω至400 Ω范围内的较低值。通过降低ADC的输入阻抗,采样保持结构引起的反冲可更快地稳定下来,从而提高线性度性能。不利的一面是输入功率增加,因为驱动满量程ADC需要更高功率。在此电路示例中,AD9467的输入阻抗降至200 Ω,以匹配ADL5565的输出阻抗,并平衡线性度与ADC输入功耗的关系。AD9467的输入阻抗通过与ADC差分输入并联放置310 Ω电阻降至200 Ω。

抗混叠滤波器设计

ADC前方的抗混叠滤波器有助于减少无用奈奎斯特区中的信号成分和噪声,从而避免造成带内混叠、防止动态性能降低。抗混叠滤波器通常用LC网络设计而成,为获得所需阻带和通带特性,源阻抗和负载阻抗必须选择得当。例如,滤波器设计可使

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- CMOS低噪声放大器中的输入匹配研究与设计(08-19)

- 实用的调频接收机电路设计(11-18)

- 意法半导体提升手机内部保护功能,为环保充电器开路(01-26)

- 如何收敛高速ADC时序(03-09)

- 低噪声、高线性度的3.5GHz LNA设计(08-14)