基于Verilog实现电器定时开关控制

1、前言

随着当今社会工作和生活节奏的加快,人们对许多电器、仪器、设备的自动化要求也越来越高,但现有的许多电器还不具备定时开启和关闭功能,许多需要在固定时间开关的装置,还需人工值守和操作,因此设计带有时钟显示功能的多个电器定时开关控制系统,具有实际意义。

2系统功能及操作

系统上电时复位,时钟显示为0时0分0秒,按下"时间"设置键设定时间,数字钟开始工作,数码管显示当前时间;按下"开启电器编号"设置键,再按下要定时开启的电器编号,对应发光二极管亮,表示设置有效;按下"电器开启时间"设置按键;再依次输入4位十进制的小时和分钟,作为开启时间;按下"电器关闭时间"设置按键,再依次输入4位十进制的小时和分钟,作为关闭时间。至此定时开关设置完成,对于电饭锅等具有保持功能的电器,则不用设置定时关闭。使用Verilog HDL编写CPLD程序,理论上可同时设置多个电器的定时自动开启,本设计可同时设置3个电器。

3硬件设计

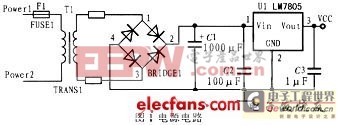

硬件设计采用Altera公司的CPLD EPM7128SLC84-6,简化了外围电路,稳定性和可靠性高,成本低。220 V、50 Hz工频电源经变压器、电桥整流后通过三端稳压器,提供工作电压,其电源电路如图1所示。

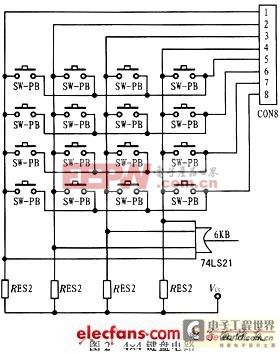

外接4×4键盘,使用较少的I/O端口线就可实现对较多按键的控制。当有键按下时,kb为低电平,CPLD的按键扫描部分采用动态扫描方式进行识别。设置14个按键,分别为0~9十个数字键和设定时间、开启电器编号、电器开启时间、电器关闭时间4个功能键,其余两个留作功能扩展。4×4键盘电路如图2所示。

本系统设计使用6个数码管显示时间,3个发光二极管标志是否定时。电器开启信号经三极管放大后接继电器,通过继电器吸合导通电源线,开启电器。

4软件设计

Verilog HDL是硬件设计人员和QuartusⅡ界面之间的交互手段,其具体物理建模能力强,设计方便,可读性好,语法类似C语言,与VHDL相比,更容易学习和掌握,与原理图设计法相比,设计和分析更容易,可避免考虑画面的布局及美观修改也方便。本设计CPLD部分完全使用Verilog HDL编写。

4.1按键扫描及键值读取

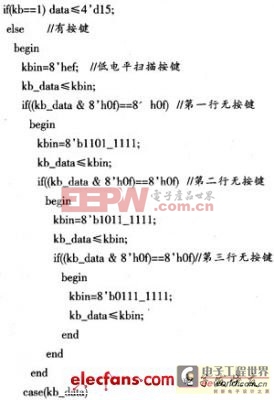

CPLD检测到kb下降沿时,表示有键按下时,为防止按键抖动,延时一段时间再检测,若确有键按下,CPLD采用低电平逐行扫描,待找到按键时,根据扫捕得到的数值,确定按键值。对于无效按键,设按键值为"15"。输入信号kb的下降沿触发对键值的读取,可保证对于每一次按键,仅作一次处理。主要程序如下:

4.2功能键的判断

程序初始化时为设定时间、开启电器编号、电器开启时间、电器关闭时间4个功能键设置对应按键值。定义功能标志寄存器fun,并使用格雷码标志各个功能,相邻两个功能的编码仅有一位不同,可避免状态跳变,比目前常用的独热码节省CPLD逻辑单元。由于本设计中寄存器fun只有5个状态,选用3位格雷码,并对编码方式进行改进。根据上一步得到的按键值判断具体要实现哪个功能,并依此设置fun的值,如下所示:

4.3数字键的判断和处理

先根据键值判断是哪一个数字键,再根据功能标志寄存器fun判断进行哪项设置。若正在进行的是时间设置,则将时间寄存器左移4位,将数字值存入低位;若为设定需要开启电器的编号状态,则电器编号数组num对应位置"1",并通过电阻使相应发光二极管点亮,否则为"0";若为设定电器开启时间状态,相应电器的开启时间寄存器timeon左移4位,将数字值存入低位;若为设定电器关闭时间状态,相应电器的关闭时间寄存器timeoff左移4位,将数字值存人低位。若为无效按键,则不进行任何操作。

4.4数字钟的工作

本系统设计作为数字钟和定时器,对计时准确性要求较高.由有源晶体振荡器提供系统时钟,可保证其稳定度。在顶层模块中对系统时钟分频,得到1 Hz时钟,作为数字钟部分行波时钟。这样减少了片内各触发器之间的时钟偏移,事实证明,对设计时序无不良影响。 先将没定的时间送人小时、分钟对应的寄存器hour和min,为了显示和用户操作方便,用6位二进制寄存器,以8421BCD码表示时间。如果秒为8'h59则秒寄存器sec清零,分钟值加1,若秒值末位为"9",则秒值末位清零,秒值十位加1。

4.5判断电器的开启和关闭

若当前时间与某个已定时的电器的开启时间相同,则开启寄存器数组on对应位输出高电平,开启对应电器;若与某个已定时的电器的关闭时间相同,则开启寄存器数组on对应位输出低电平,关闭对应电器。

4.6显示

对应不同的状态,数码管显示不同值。时钟设置状态,显示当前时间;开启电器编号设置状态,显示欲开启的电器编号;电器开启时间设置状态,屁示电器应开启的时间;电器关闭时间设置状态

- PCM串行数据流同步时钟提取设计(02-25)

- 一种数模混合SoC设计协同仿真的验证方法(04-09)

- 基于FPGA的∑-△D/A转换器的设计与实现(04-23)

- 基于ISP芯片的可编程数字移相器设计(06-23)

- 一种锁定相位编程可调全数字锁相环设计(06-24)

- 基于Virtuoso平台的单片射频收发系统电路仿真与版图设计(07-18)