H.264_AVC视频编码变换量化核实现

2003年推出新的视频压缩标准H.264 /MPEG-4 -10AVC,简称H.264/AVC。H.264/AVC采用一系列新的压缩方法[1],可获得更好的压缩效果,其压缩率达到以往标准的1.5~2倍。因此,基于这一标准的相关研究和硬件实现具有重要的意义。视频压缩硬件实现的关键是编解码模块,其中尤以编码模块最为核心。本文主要研究编码模块中的4×4整数变换量化核,提出硬件实现的优化方法,并采用Verilog HDL语言进行硬件设计和综合。

1 4×4整数变换量化核的原理

在以前的视频编码标准如MPEG-2和H.263中,对于预测的残差数据都是采用8×8离散余弦变换(DCT)[1]作为变换的基本运算操作;而在H.264/AVC编码标准中,则采用类似DCT变换形式的基于4×4 像素块的整数变换。由于变换块的尺寸缩小,运动物体的划分更精确,而且运动物体边缘处的衔接误差大为减小。

对于整数变换方式,4×4像素块的变换公式[3]为:

式中,(CXCT)是二维变换核,Ef是缩放因子矩阵,符号表示CXCT矩阵里的每个元素和Ef矩阵中相同位置的元素相乘,a=1/2,b=

。为了更有效地压缩数据,需要利用量化的方法对变换后的数据进行有损压缩。同时,由于整数变换需要利用矩阵行向量的归一化因子进行系数缩放处理,为降低变换的运算量,在H.264/AVC标准中将变换的系数缩放并进行量化运算处理,避免了复杂的实数运算和除法运算,更有利于硬件的实现。

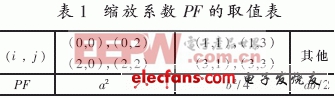

对于量化方式,正向量化运算可由如下公式[3]实现:

式中, Zij为量化后的系数;Wij为变换矩阵W=CXCT中的元素;MF=

·2q,PF 称为缩放系数,根据元素在阵列块中的不同位置,其取值如表1所示,Qstep为量化步长,由0至51共52个量化参数QP决定,QP增加1, Qstep增加12.5%; q=15+QP/6,QP/6取整数;对于帧内宏块f取2q/3,帧间宏块f取2q/6。需要指出的是,MF的值可根据PF和QP的取值经简单计算得到,并可形成格,通过查表方式便可实现硬件运算,并有效地提高了运算速度。

2 4×4整数变换量化核的优化设计

为进一步提高硬件运算速度,减少硬件开销,设计中采用了如下优化方法:

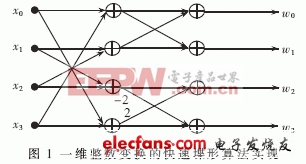

(1)在求取变换阵W=CXCT时,根据变换的对称性,将X的列变换(矩阵左乘)与行变换(矩阵右乘)分开实现,把二维变换分割为两次一维变换,并采用快速堞形算法[4]来实现。一维变换的快速算法实现如图1所示,其中的列变换可用如下算式表示:

对于每列变换,需要进行8次加法和2次移位运算,而行变换则可根据矩阵转置的性质ABT=(BAT)T,将经过列变换后的结果矩阵先进行转置,再采用相同的变换形式运算。这样对4×4点数据做一次变换,只需通过8×8次加法和2×8次移位运算便可完成。

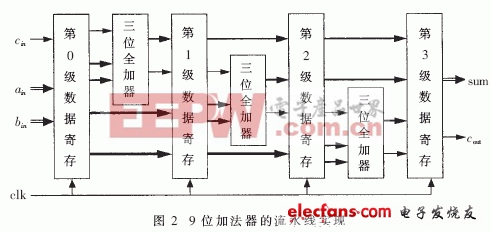

(2) 针对不同运算的位宽需要,设计专用的加法器和乘法器。本文对整数变换中的加法器采用三级流水线加法器,实现9位加法,每级流水线完成三位超前进位加法,将逻辑延迟限制在三位加法器之内。图2给出了9位加法器的流水线实现框图。选用EPF10K10LC84-3作为适配器件,经过Synplify Pro 7.3综合,结果表明这种加法器具有较优的最高工作频率和硬件开销。如表2所示, 常规加法器的最高工作频率为37.0MHz,消耗资源却为28LC,而经过优化的三级流水线加法器在消耗资源增加不多的情况下,其最高工作频率相比常规加法器提高了257%,达到94.5MHz。

在量化过程中,对于给定的量化参数QP, MF只有三种取值,因此乘法实现可以采用无符号数乘法运算,乘法结构则采用16×14位加法树乘法器。这样,在提高运算速度的同时节约了芯片面积。

(3)对于f的计算,在不影响运算精度的情况下本文采用近似处理。为了避免除法运算,将f的计算式变形,即:

f=2q/3=(215/3)×2m≈[(215+1)/3]×2m≈10923×2m

式中, m取值为0~8,具体由相应的QP给出。由于f在完成加法运算后其结果还需左移q位,所以计算精度不会受影响。这样,对f的计算只需进行移位操作。

3 4×4整数变换量化核硬件实现

基于上述算法原理及其设计,本文首先对4×4整数变换量化模块进行C语言编程,验证了该模块所采用算法的正确性。然后采用Verilog HDL语言描述4×4整数变换和量化核(帧内模式)的硬件功能,并通过仿真软件Modelsim SE 5.7进行功能仿真,验证了该模块输出结果与设计要求相一致。最后采用Synplify Pro7.3综合工具,并以Altera公司的Stratix系列FPGA作为主要目标适配器件进行综合。

4×4整数变换量化核的二大子模块的综合结果如表3所示,表中同时给出经本文优化设计前后的综合结果作为对比。可见,经本文采用的三种优化设计处理后,在硬件开销改变不大情况下,变换子模块的最高工作频率达到59.4MHz,是未优化前的1.73倍,而量化子

- 利用阻性负载增强LNA稳定性(下)(11-19)

- DPA-Switch为应对PoE受电设备设计挑战提供有效解决方案(11-06)

- 利用阻性负载增强LNA稳定性(上)(11-19)

- PCB电源供电系统的分析与设计(11-21)

- 基于CH371的实用USB接口设计(01-23)

- Ni-MH 9V 充电电池(01-05)