ARM的未来低功耗系统设计发展之路

每一名系统设计人员都理解功耗和性能的相对关系:您的应用需要的计算性能越高,设计的功耗也就越高。但是,新一类应用对这一规则发出了挑战。智能电话设计人员希望同时实现PC级峰值应用速率以及更长的电池使用寿命。嵌入式系统规划采用智能传感器以满足严格的数据分析要求,安全的连接互联网,但是要求最大限度的降低功耗。在传统的思路中,这些明显是无法实现的。但是,ARM工程师在6月份设计自动化大会(DAC)上的发言表明,CPU知识产权(IP)带头企业的发展方向却是将这些不可能变为可能。

当然,ARM从开始出现便一直专用于低功耗计算。在其DAC主题发言中,ARM创始人之一Mike Muller从小剑桥计算机业余爱好供应商Acorn Computer公司一个芯片设计人员小组在1980年早期提出的问题开始,追溯了体系结构的发展:他们能使用RISC原理来开发16位微处理器,其性能超越个人计算机中的传统芯片吗?这一问题的答案是Acorn RISC机——ARM今后发展壮大的萌芽。

Acorn公司最初的成功源自高效的使用逻辑门和寄存器,主要是在简洁的RISC体系结构的支撑下实现的。尽量减少每一操作所需的逻辑转换数也一直是ARM套件的关键工具。但是,随着公司在研发预算上的增长,以及公司影响的扩大,ARM设计人员开始在降低每一操作所需的功耗上寻求更好的工艺和电路技术。异步设计、低功耗工艺技术、精细粒度时钟选通、电源选通以及动态电压频率调整(DVFS)等都成为工具套件的一部分。

Muller说,今天,ARM增加了新工具:超精细粒度电源选通,例如,以非常低的电压进行工作等。但是,完全不同的发展方向将产生完全不同的技术:异构多核计算和虚拟化的概念——这是来自服务器领域的理念。

扩展低端

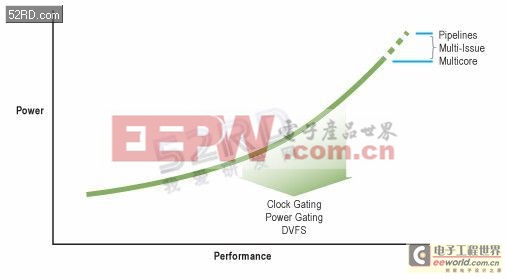

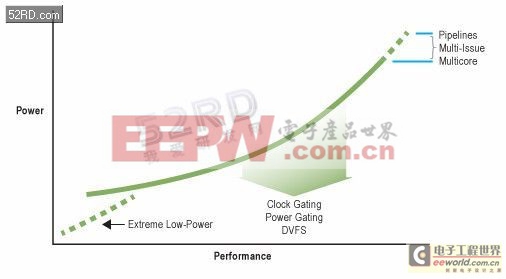

在评估功耗和性能的一张图(图1)上,不同的技术扩展了这张图中不同位置的曲线。进一步使曲线向高性能方向扩展的技术包括,深度流水线、高时钟频率以及多核簇等。这些方法完全不同于功耗管理技术,功耗管理技术将整条曲线向低功耗方向下拉。两者都具有的不同之处是新出现的一类技术,使曲线向下向左:超低功耗,低速计算。

Muller说,这是长寿命电池和低功耗的范围。这里的问题是,怎样以很低的能量来完成少量的计算。今天,异步CPU毫无争议的占据了这一领域的制高点。只有当信号出现变化时才消耗动态功耗——而不是在每一次时钟转换时,因此,如果异步电路能够克服其开销逻辑的能耗成本,它将大幅度降低动态功耗。

但是,在高级工艺节点,特别是在较低时钟频率时,静态功耗会大于动态功耗。因此,Muller关注的重点不是动态功耗,而是泄漏问题。

在高级工艺节点唯一降低泄漏真正有效的手段是降低工作电压。Muller指出,问题是,当我们减小了器件尺寸后,很难调整晶体管阈值电压Vt。我们目前所处的情景是,无法再进一步调整Vt以减小供电电压,晶体管不能工作在传统的饱和模式下。取决于所采用的传统CMOS电路,一旦退出饱和模式后,会产生很强的源极漏极电流,还会进行快速开关。

Muller解释说,但这并不意味着一点办法都没有。我们还是能够减小工作电压VDD,使电流足够快,直至系统满足性能要求。只要不太靠近Vt,我们可以采用的技术是DVFS。而Muller则阐述了更激进的一些想法。

第一个是关断所有电源,把泄漏降到零。很显然,粗粒度电源选通是有效的方法——例如,没有使用的模块。Muller指出,消耗很大的电能来迅速执行一项任务,然后关断电源,这样做通常可以节省能量。但还有更有趣的想法。

非常慢的运行

大部分系统都有一些不需要高速运行的任务,只需要完成它们就可以了。一般会由于某一原因而保持这些任务处于工作状态,因此,系统不能简单的接通,让它们工作,然后,再次关断。有针对减小这些任务的泄漏功耗而采取的节能方法。

ARM展示了当模块工作在较长的时钟周期中时,您可以在时钟转换期间关掉组合逻辑电源。如果时序正确,保持时间之后关掉供电,在逻辑需要传播新状态时再恢复供电,这样不会改变寄存器中的序列。根据某些信息来源,这一方法能够把泄漏减小25倍。由于逻辑电源网络实际上成为自己的信号通路,因此,这一“子时钟电源选通”(图2 )方法会增加一些晶体管,增大动态功耗,当然也会增加时序收敛的复杂度。但是,在电路中降低了25倍,这的确是非常重要的方法。

这就带来了怎样降低寄存器本身泄漏的问题,这涉及到在时

- 基于ARM核的音频解码器单芯片系统(01-05)

- 美国国家半导体SolarMagic技术为公寓太阳能工程增加22.6%的发电量(06-21)

- 基于FPGA的多通道数据采集系统设计(09-30)

- 心电模拟波形发生系统的设计(06-15)

- 基于ARM和DS18B20的数字测温系统(10-21)

- 掉电保护在嵌入式系统中的设计应用(01-05)