如何满足复杂系统的高性能时序需求

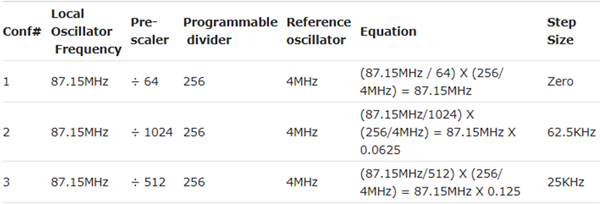

率信道增加到较高频率信道。通过改变预分频器和可编程分频器的值,微控制器可以调整步长。

步长=(本地振荡器频率/预分频器)X(可编程分频器/参考振荡器)

表1 所示为部分配置。

通过I2C 接口进行系统内编程

系统内编程可为系统设计实现快速有效的迭代。编程数据序列可通过SCL和SDA引脚传送到时钟器件,把操作顺序编程至板载微控制器(主设备)中,通过命令和数据在运行时与从机时钟进行交互。

此处为系统示例,其中时钟信号必须以采样率的倍数为准。该时钟频率在155.52MHz和156.25 MHz两组频率之间变动。这意味着驱动串行控制器的时钟必须能够在这两个值之间灵活切换。微控制器主设备可以访问并修改写入易失性存储器的PLL配置,从而满足这两个频率需求。

通过频率选择(FS) 引脚更新配置

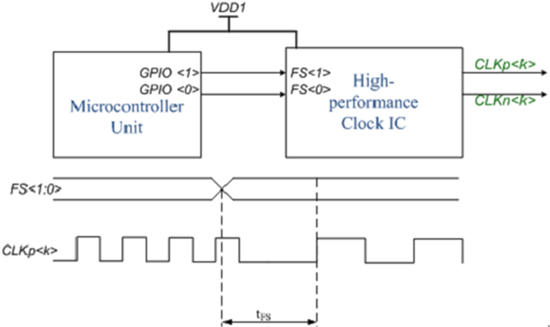

高性能时钟设备支持包含个性化配置的多个用户配置文件。在FS引脚转换方面,高性能时钟器件具有两个时序规格- 快速切换和慢速切换。

快速切换适用于输出ON/OFF 、输出分频值变化,以及输出MUX 设置更改。慢速切换则适用于更改PLL 参数(包括PLL ON/OFF)。顾名思义,快速切换中的输出变化更快,而慢速切换的速度较慢。两种切换类型都可以打开或关闭输出,并且不出丝毫差错。图4 所示为FS 与输出时钟之间的时序关系。

图4:频率选择操作。

外部复位操作:

当外部复位生效时,时钟IC进入低功耗模式。输出和I2C总线信号处于高阻抗(HI-Z) 状态,直到取消外部复位并完成初始化。外部复位重启易失性存储器内容,存储在非易失性存储器中的配置则被复制到易失性存储器。当需要重新初始化任意一个系统中运行的应用程序时,该功能将被使用。

压控晶体振荡器(VCXO) 操作:

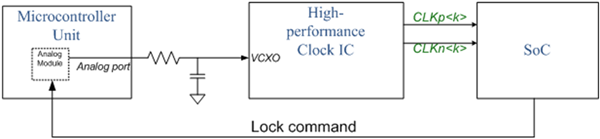

对某些应用而言,输出时钟频率应通过使用模拟反馈跟踪输入数据流。如图5所示,时钟IC作为大锁相环的一部分。ASIC或SoC负责跟踪输入流、计算误差并产生PWM信号(通常来说),随后将误差信息反馈至本地时钟发生器以进行频率调谐。

图5:VCXO 示例电路。

VCXO功能能够修改PLL频率,因此频率牵引不依赖于晶体特性、温度、电压或设备工艺。VCXO调制是线性、精准调制。也可以使用时钟参考。通过微控制器的内置模拟模块,VCXO的控制逻辑精准到小数点后6位。

作为I2C主设备,微控制器将配置写入时钟IC 的内部易失性存储器并控制PLL。因此,通过板载MCU-IC组合可以实现系统时钟频率的动态更新。开发人员可以使用可编程微控制器,为高性能时钟IC提供控制逻辑。这可以减少对板载IC和走线数量的需求,使得整个系统设计更加紧凑。

微控制器配备强大IDE工具,可以加速应用开发。集成可编程片上系统(PSoC)器件可进一步简化设计并有助于降低整体产品成本。有关高性能时钟IC设计的更多详细信息,请参阅4-PLL扩频时钟发生器入门以及扩频时钟发生器的设计最佳实践。

锁相环 相关文章:

- 精密频率合成技术助力多通道频率合成器的应用(06-08)

- 如何设计并调试锁相环PLL(03-19)

- 锁相环的工作原理及设计方法(06-19)